TSMC reveló las principales actualizaciones de la hoja de ruta para su familia de tecnologías de proceso N3 (clase de 3 nanómetros) en su Simposio de Tecnología de América del Norte 2023 esta semana. Como el nodo final de alto rendimiento de TSMC basado en transistores FinFET, N3 durará muchos años e incluirá múltiples versiones, incluido N3P, un encogimiento óptico de N3E que mejora el rendimiento y N3X centrado en el rendimiento para aplicaciones HPC que toleran altas fugas y potencia. .

La producción en masa de TSMC en su tecnología de proceso N3 (también conocida como N3B) ya está en marcha, pero este nodo utiliza litografía ultravioleta extrema en hasta 25 capas e incluso puede usar patrones dobles EUV, lo que lo convierte en un nodo particularmente costoso de usar. Como resultado, TSMC espera que la mayoría de sus clientes usen N3E, que puede usar EUV en hasta 19 capas, no usa EUV de doble patrón, tiene una ventana de proceso más amplia y mejores rendimientos. N3E, que se utilizará para la fabricación de gran volumen en el segundo semestre de 2023, también será la base para la evolución adicional de 3nm de TSMC.

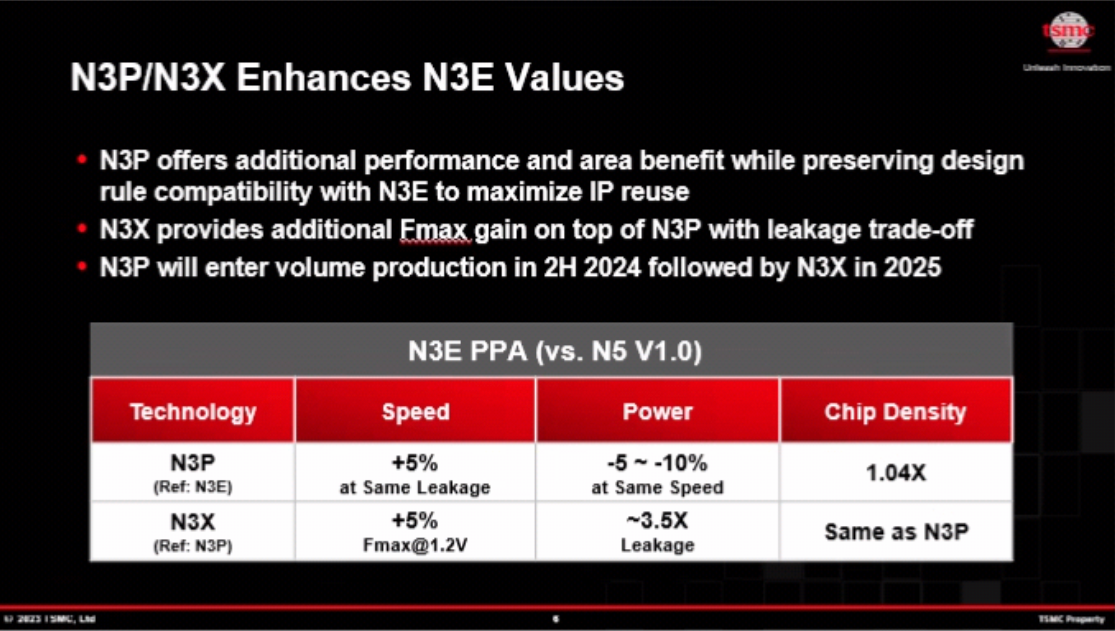

El primer paso en esa evolución será N3P. Esta tecnología será en gran medida una reducción óptica de N3E que contará con algunas otras mejoras que permitirán un aumento del rendimiento del 5 % con la misma fuga, una reducción de potencia del 5 % al 10 % con los mismos relojes y una densidad de transistores un 4 % más alta para un ‘ chip mixto que consta de 50 % de lógica, 30 % de SRAM y 20 % de circuitos analógicos.

Como una reducción óptica de N3E, N3P conserva sus reglas de diseño, lo que permite a los diseñadores de chips reutilizar la IP de N3E en el nuevo nodo. Esto es bastante importante ya que las empresas de diseño de IP como Ansys, Cadence y Synopsys ya tienen una gran cantidad de IP dirigida a los chips N3E. Mientras tanto, el encogimiento óptico implica mejoras en la densidad para todo tipo de transistores y circuitos, incluido SRAM, un tipo de circuito que ha tenido problemas para encogerse en los últimos años (algo particularmente malo para los diseños modernos con uso intensivo de SRAM). N3P estará listo para la producción en masa en 2024.

Después de N3P, TSMC planea expandir aún más su familia N3 y ramificarla en aplicaciones informáticas de alto rendimiento como CPU y GPU con N3X. Se prevé que este proceso de fabricación proporcione frecuencias al menos un 5 % más altas en comparación con N3P y también permita voltajes considerablemente más altos, lo que aumentará aún más los relojes a costa de una mayor fuga general.

| Fila 0 – Celda 0 | N3X frente a N3P | N3P frente a N3E | N3E frente a N5 | N3 frente a N5 |

| Mejora de la velocidad a la misma potencia | +5 % Fmáx a 1,2 V | +5% | +18% | +10% ~ 15% |

| Reducción de potencia a la misma velocidad | ? | -5% ~ -10% | -32% | -25% ~ -30% |

| Densidad lógica | mismo | 1.04x | 1.7x | 1,6x |

| Inicio HVM | 2025 | 2S 2024 | T2/T3 2023 | 2S 2022 |

TSMC afirma que su nodo N3X puede manejar al menos 1,2 V, un voltaje notablemente alto para una tecnología de fabricación de clase 3nm. Esto viene con una compensación considerable, ya que TSMC anticipa un asombroso aumento del 250 % en la fuga de energía en comparación con N3P. Esto destaca que N3X es principalmente adecuado para CPU HPC y requerirá que los diseñadores de chips tengan cuidado al desarrollar sus chips de mayor rendimiento que consumen mucha energía, como CPU de centro de datos y GPU de cómputo.

En términos de densidad de transistores, N3X coincidirá con las capacidades de N3P. TSMC no ha especificado si su N3P y N3E tendrán reglas de diseño compatibles, lo que deja espacio para la intriga sobre si los diseños se pueden transferir entre los dos nodos.