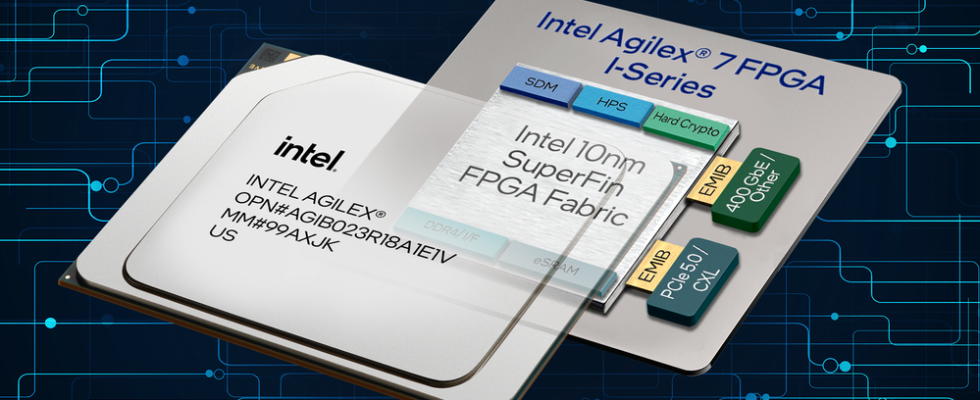

Intel anunció hoy su familia Agilex 7 M-Series de productos Field-Programmable Gate Array (FPGA), duplicando su nodo de fabricación SuperFin de 10 nm revitalizado. Citando la creciente demanda del mercado de soluciones FPGA como coprocesadores para redes, centros de datos, computación de alto rendimiento (HPC), computación en la nube y otras aplicaciones, Intel promete una mayor flexibilidad (principalmente debido a la naturaleza inherentemente programable de FPGA) y mayores capacidades de escalado que nunca. Los FPGA Agilex 7 de Intel presentan un nuevo chiplet como parte de su arquitectura heterogénea de matriz múltiple, el R-Tile, que es responsable de brindar las últimas tecnologías de conectividad, a saber, compatibilidad con PCIe 5.0 y CXL, en bloques de IP codificados y acelerados por hardware. .

El nuevo chiplet heterogéneo R-Tile es la estrella del espectáculo para Intel, lo que le permite reclamar el título de la única familia de FPGA que cuenta con la certificación para la velocidad de datos PCI-SIG 5.0 x16 completa. Xilinx, que ahora se fusiona con AMD, sería un ejemplo de otro desarrollador de FPGA de vanguardia, por lo que aquí se tiene la sensación de una carrera ganada por Intel.

Curiosamente, Intel parece estar redoblando su apuesta por la separación entre los productos FPGA y CPU. Tal vez sea el resultado de sus incursiones anteriores en la integración, de las cuales solo quedan historias de fantasmas de silicio. AMD parece estar mucho más seguro de que ha resuelto el caso: la compañía aparentemente está buscando incorporar capacidades FPGA en las CPU EPYC de la compañía a principios de este año. Ahora, eso no cimenta una separación entre ambas compañías: AMD también puede estar buscando una integración similar a un chiplet, ya sea verticalmente a través del apilamiento 3D o incorporando IP segregada específica de FGPA en un chip separado.

La idea general de los FPGA es su flexibilidad inherente, que permite a los desarrolladores iterar rápidamente en la disposición del circuito y los bloques de procesamiento para adaptar el FPGA a las cargas de trabajo específicas en cuestión. Al ser un hardware más especializado, los FPGA se pueden usar para acelerar las cargas de trabajo que no dependen de la CPU, lo que libera valiosos recursos de la CPU para sus tareas específicas (como la rotación de máquinas virtuales en una instalación basada en la nube) en lugar de aprovechar su potencia más baja. eficiencia (el costo de sus capacidades de procesamiento generalizadas).

R-Tile de Intel trae esencialmente los bloques IP acelerados por hardware responsables de manejar los protocolos PCIe 5.0 y CXL 1.1/2.0 en su familia Agilex 7 FPGA. Eso debería generar mejoras significativas en la eficiencia energética y el rendimiento de datos, que son elementos importantes para reducir el costo total de propiedad (TCO) para instalaciones de alto rendimiento. Pero con estas opciones, siempre hay compensaciones: Intel está agregando otro bloque de hardware de función fija a un producto cuya conveniencia radica en que sea programable. Programable Después de todo, el área es el mantra del comprador de FPGA.

También vale la pena mencionar que, como producto, R-Tile dice específicamente «Estoy aquí para reducir la carga en sus CPU y brindar un mayor rendimiento». Pero otra respuesta a esa necesidad no se trata de mover las funciones de la CPU hacia un FPGA; es simplemente aumentar la cantidad de recursos de CPU disponibles. Y eso podría hacerse con más CPU (lo que podría tener sentido para algunos instaladores) o núcleos de CPU adicionales. Después de todo, la serie Agilex 7 M de Intel se comercializa específicamente para los Xeon escalables de cuarta generación de Intel, y esos no son los reyes del conteo de núcleos en ninguna forma.

La apuesta de Intel es que las preguntas anteriores tienen una respuesta y que sabe la respuesta: es por eso que presentó Agilex 7. La respuesta de Intel es que los consumidores quieren eliminar la sobrecarga de la CPU moviéndola a un paquete FPGA. Quieren el mejor rendimiento/vatio posible (uno de los mayores contribuyentes al alto costo total de propiedad), por lo que moverán las cosas a donde sean más rápidos. Afortunadamente, este movimiento beneficia a Intel de otras maneras. Para la empresa, es una cuestión de su propia eficiencia y, como tal, una cuestión de costes.

Ahí es donde realmente brilla el puente de interconexión multi-die integrado (EMIB) de Intel. Como el «pegamento» proverbial que mantiene unidos los bloques de procesamiento dispares, EMIB permite a Intel separar aún más los bloques de IP en el nivel de fabricación, aumentando la eficiencia del troquel y reduciendo la ecuación del costo total por oblea (y el costo por chip resultante).

Para el consumidor, teóricamente también reduce los costos: el sueño de Intel (y el de la industria) es poder mezclar y combinar diferentes bloques de IP de hardware (del mismo proveedor, o incluso de múltiples proveedores y procesos de fabricación), lo que significa que los clientes solo tienen que pagar para el silicio que realmente usarán, con las especificaciones que realmente usarán. En cierto sentido, esto convertiría a cada chip en un FPGA.

Con todo eso en mente, es posible que el Agilex 7 con R-Tile de hoy sea tanto un nuevo producto FPGA como un nuevo elemento básico en el catálogo de Intel Foundry Services (IFS). De cualquier manera, mueve a Intel en la dirección que quiere, y necesita, ir. Y eso es sólo un buen negocio.