Por qué es importante: El escalado de transistores y la potencia trasera son claves para ayudar a satisfacer la demanda cada vez mayor de informática más potente. Año tras año, Intel satisface esta demanda informática, lo que demuestra que sus innovaciones seguirán impulsando la industria de los semiconductores y seguirán siendo la piedra angular de la Ley de Moore. El grupo de Investigación de Componentes de Intel constantemente traspasa los límites de la ingeniería al apilar transistores, llevando la energía trasera al siguiente nivel para permitir un mayor escalado de transistores y un rendimiento mejorado, además de demostrar que se pueden integrar transistores hechos de diferentes materiales en la misma oblea.

Los anuncios recientes de la hoja de ruta de la tecnología de procesos que destacan la innovación de la compañía en el escalamiento continuo (incluyendo energía trasera PowerVia, sustratos de vidrio para empaques avanzados y Foveros Direct) se originaron en Components Research y se espera que estén en producción esta década.

Cómo lo hacemos: En IEDM 2023, Components Research mostró su compromiso de innovar en nuevas formas de colocar más transistores en el silicio y al mismo tiempo lograr un mayor rendimiento. Los investigadores han identificado áreas clave de I+D necesarias para seguir escalando mediante el apilamiento eficiente de transistores. Combinados con la alimentación y los contactos traseros, estos serán grandes avances en la tecnología de arquitectura de transistores. Además de mejorar la entrega de energía trasera y emplear nuevos materiales de canal 2D, Intel está trabajando para extender la Ley de Moore a un billón de transistores en un paquete para 2030.

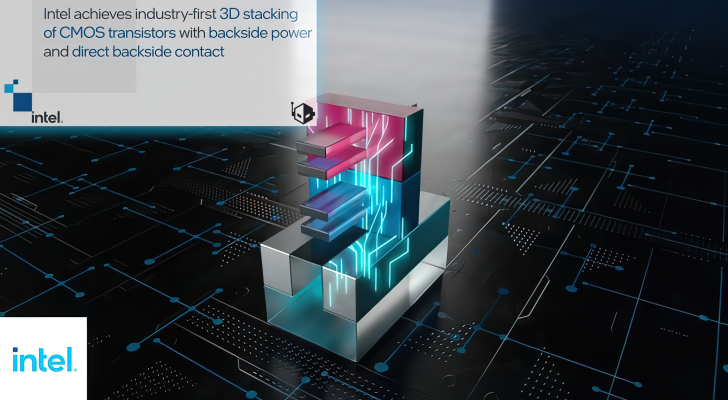

Intel ofrece transistores CMOS apilados 3D innovadores y pioneros en la industria combinados con alimentación y contacto traseros:

- La última investigación sobre transistores de Intel presentada en IEDM 2023 muestra una primicia en la industria: la capacidad de apilar verticalmente transistores de efecto de campo complementario (CFET) en un paso de puerta reducido a 60 nanómetros (nm). Esto permite obtener beneficios de eficiencia y rendimiento del área al apilar transistores. También se combina con alimentación trasera y contactos traseros directos. Subraya el liderazgo de Intel en transistores de puerta integral y muestra la capacidad de la empresa para innovar más allá de RibbonFET, colocándola por delante de la competencia.

Intel va más allá de cinco nodos en cuatro años e identifica áreas clave de I+D necesarias para continuar escalando transistores con entrega de energía trasera:

- PowerVia de Intel estará listo para su fabricación en 2024, lo que será la primera implementación de entrega de energía trasera. En IEDM 2023, Components Research identificó caminos para extender y escalar la entrega de energía trasera más allá de PowerVia, y los avances clave en los procesos necesarios para habilitarlos. Además, este trabajo también destacó el uso de contactos posteriores y otras interconexiones verticales novedosas para permitir el apilamiento de dispositivos con eficiencia de área.