Intel detalló el lunes la implementación de una red de entrega de energía trasera (BS PDN) que formará parte de sus procesos de fabricación Intel 18A y 20A (18/20 angstroms, 1.8/2.0nm-class). Además, la compañía también reveló más información sobre los beneficios que esta tecnología brinda para su nodo interno Intel 4 + PowerVia diseñado específicamente para mejorar BS PDN.

Entrega de energía trasera

Las tecnologías de fabricación 18A y 20A de Intel presentarán dos innovaciones clave: los transistores de efecto de campo (GAAFET) de puerta de enlace RibbonFET y la red de suministro de energía trasera PowerVia. Las ventajas de los transistores GAA se han discutido anteriormente y están más allá del alcance del anuncio de hoy. En su lugar, nos centraremos en la entrega de potencia trasera.

El riel de alimentación de la parte trasera tiene como objetivo separar la alimentación y el cableado de E/S, desplazando las líneas de alimentación a la parte posterior de la oblea. Este método aborda problemas como el aumento de las resistencias en el back-end-of-line (BEOL), mejorando en última instancia el rendimiento de los transistores y reduciendo su consumo de energía. También elimina cualquier posible interferencia entre los cables de datos y de alimentación y aumenta la densidad del transistor lógico.

Con el tiempo, BD PDN se convertirá en una función de chip estándar, pero por ahora Intel lo considera una gran innovación similar al silicio tenso a 90 nm en 2003, la puerta de metal high-K basada en hafnio a 45 nm en 2007 y FinFET a 22 nm en 2012. .

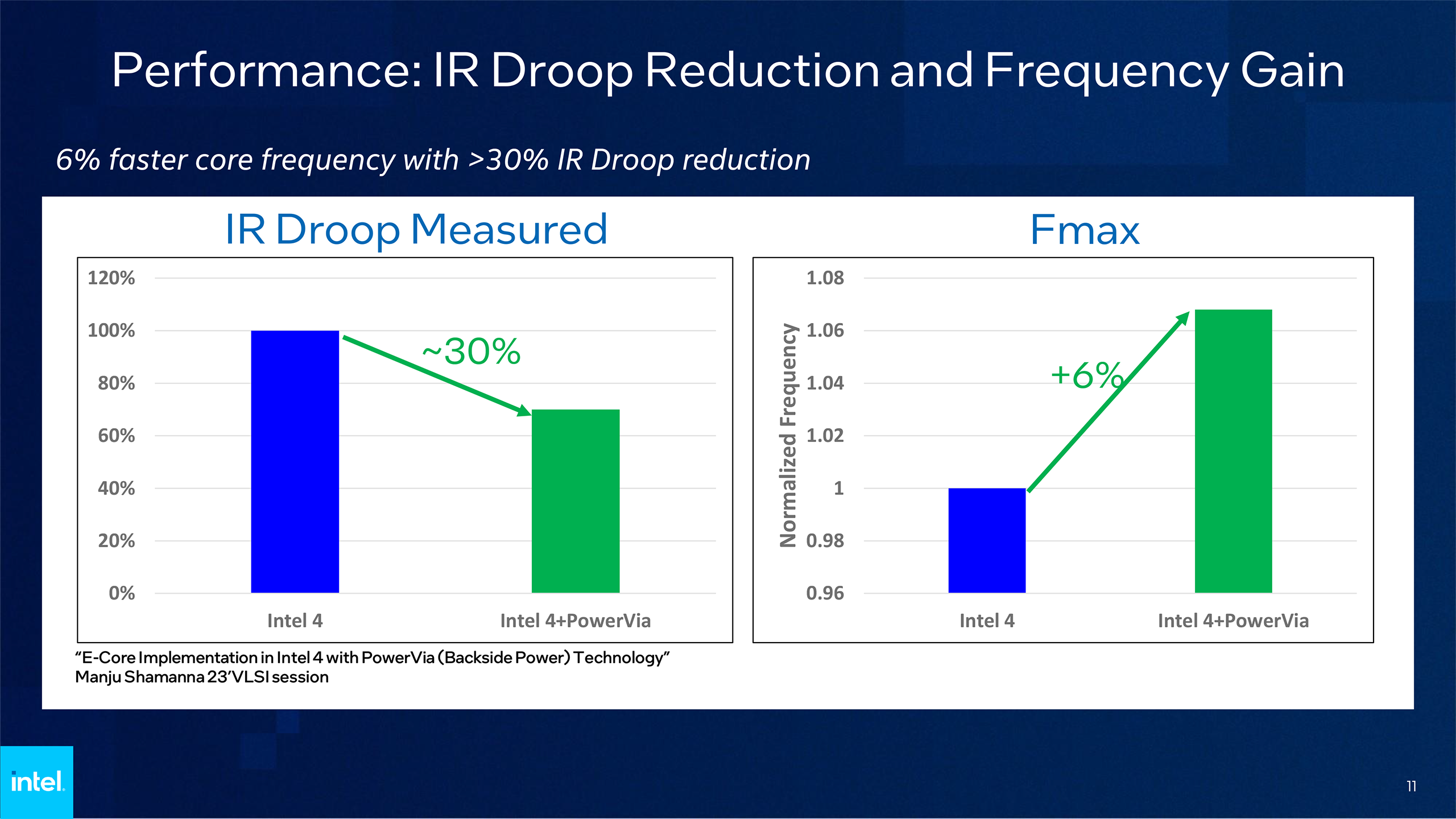

Intel dice que cuando se implementó en un chip de prueba en un nodo de proceso interno, su PDN posterior le permitió aumentar la velocidad del reloj en más del 6 %, redujo la caída del voltaje IR en un 30 % y aumentó la utilización de la celda en grandes áreas de su matriz E-core. a más del 90%. A pesar de los beneficios, implementar y construir una entrega de energía trasera es un desafío por varias razones.

Creación de PowerVia Parte trasera PDN

La construcción de una PDN trasera es muy diferente de la entrega de energía frontal tradicional. La producción de incluso los chips más avanzados es bastante sencilla en estos días. La fabricación de cada oblea comienza desde la capa de transistor M0 más compleja con pasos de tan solo 30 nm (para el nodo Intel 4) utilizando las herramientas de fabricación más sofisticadas, como los escáneres EUV. Luego, los fabricantes de chips construyen capas de transistores menos complejas encima de la primera, aumentando gradualmente los tamaños a medida que necesitan conectar todas las capas y alimentar todos los transistores.

Los cables físicos reales para E/S y alimentación parecen gigantes en comparación con las capas de transistores, y se vuelve más difícil y costoso enrutarlos correctamente con cada nueva generación.

Procesar una oblea con chips con PowerVia BS PDN de Intel implica producir todas las capas lógicas complejas, así como cables de señal, luego voltear la oblea y construir la red de suministro de energía «sobre» la lógica. Sobre el papel, tal ‘giro’ no parece gran cosa. Sin embargo, agrega una gran cantidad de pasos de proceso, incluida la eliminación del «exceso» de silicio de la oblea para construir el PDN sobre los transistores lógicos, limpieza de CMP, metrología, litografía y grabado, por nombrar algunos.

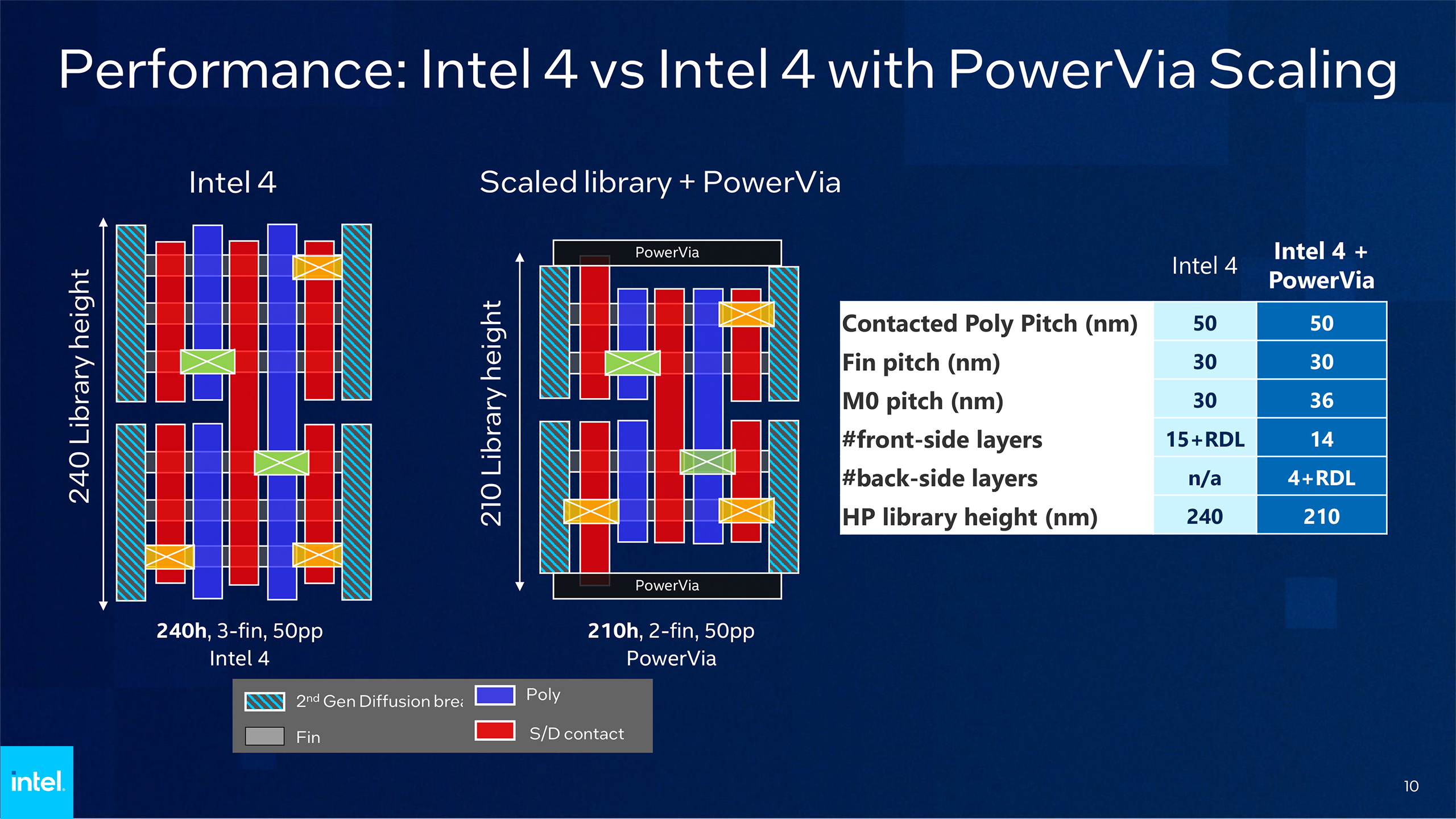

Es posible que un ciclo de proceso de este tipo no requiera las herramientas más avanzadas de la fábrica, pero aun así cuesta dinero. De hecho, una diapositiva de Intel indica que la tecnología de proceso Intel 4 utiliza 15 capas metálicas y una capa de redistribución (RDL), mientras que Intel 4 + PowerVia utiliza 14 capas laterales frontales, cuatro capas laterales traseras y una RDL, lo que aumenta el número total de capas. a 18+RDL.

«Los transistores se construyen primero, como antes, y luego se agregan las capas de interconexión», dijo Ben Sell, vicepresidente de Desarrollo de Tecnología de Intel. «Ahora la parte divertida: voltea la oblea y pule todo para exponer la capa inferior a la que se conectan los cables». […] para el poder será conectado. Lo llamamos tecnología de silicio, pero la cantidad de silicio que queda en estas obleas es realmente pequeña».

Hay varios factores a considerar con un PDN trasero. En primer lugar, cambia drásticamente el proceso de fabricación, por lo que Intel tuvo que encontrar una manera de garantizar altos rendimientos a pesar de los cambios radicales. En segundo lugar, Intel tenía que asegurarse de que la PDN trasera fuera tan confiable como su PDN actual y funcionara según lo previsto. En tercer lugar, dado que los cables de E/S y de alimentación ahora están ubicados en ambos lados de los transistores, será más difícil enfriar los chips en el futuro. En cuarto lugar, se vuelve significativamente más difícil depurar chips ya que ahora Intel tiene que eliminar las interconexiones de alimentación traseras para acceder a las capas de transistores.

También hay otra peculiaridad sobre el proceso PowerVia de Intel. Debido a que Intel elimina el exceso de silicio de la parte posterior de la oblea, cree que pierde rigidez, razón por la cual une una oblea portadora en el lado de la señal de la oblea para mantener unida la construcción. Esa oblea portadora también se adelgaza eventualmente, pero su adición también es un paso de proceso complicado (y probablemente necesario).

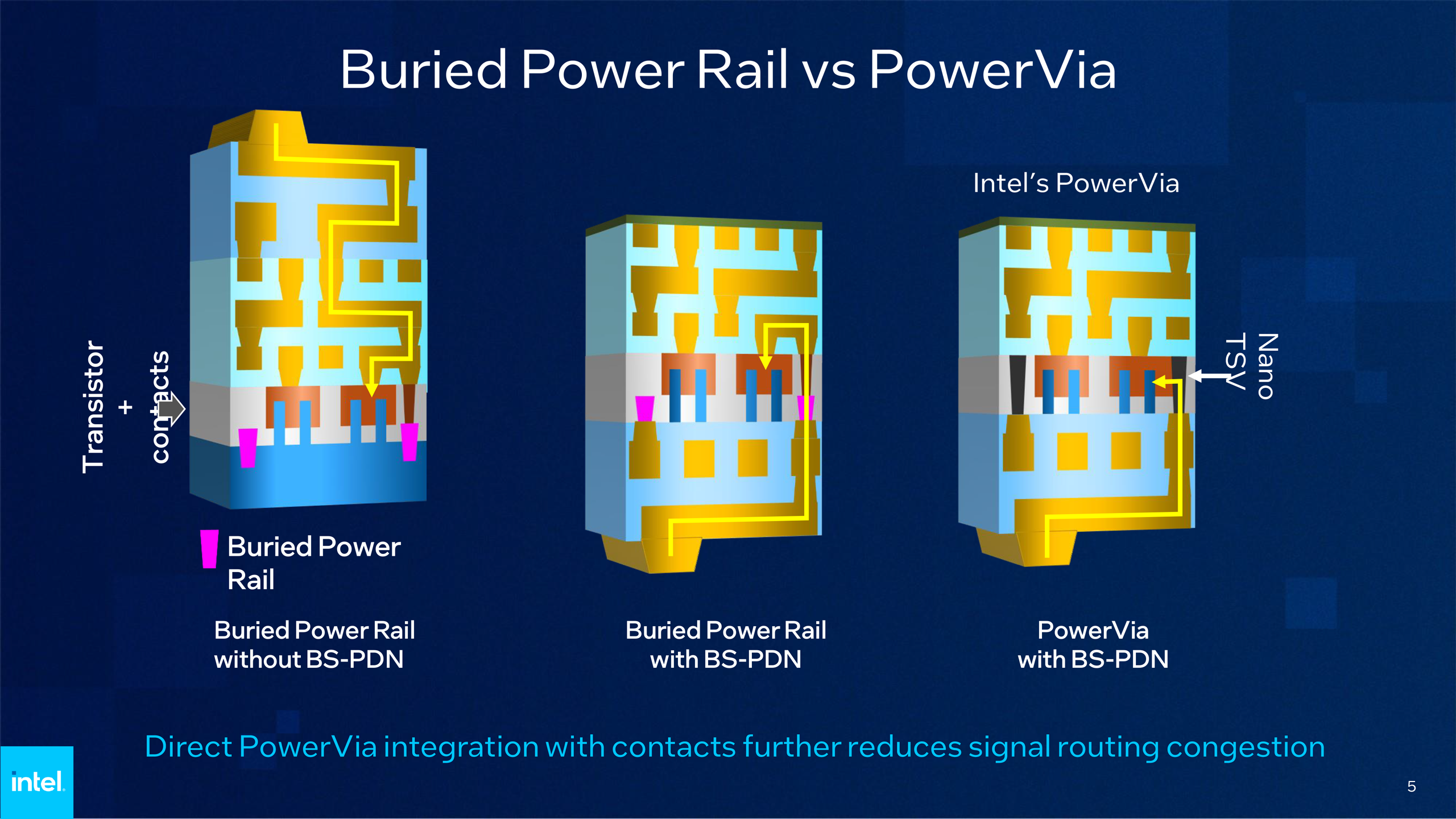

Otra cosa sobre el PDN trasero PowerVia de Intel es que no utiliza rieles de alimentación enterrados con BS PDN, sino que se basará en nanoescala a través de vías de silicio (TSV) para entregar energía directamente a la capa del transistor. Esta es obviamente la razón por la cual la compañía llama a su tecnología PowerVia.

Prueba de la red de suministro de energía trasera

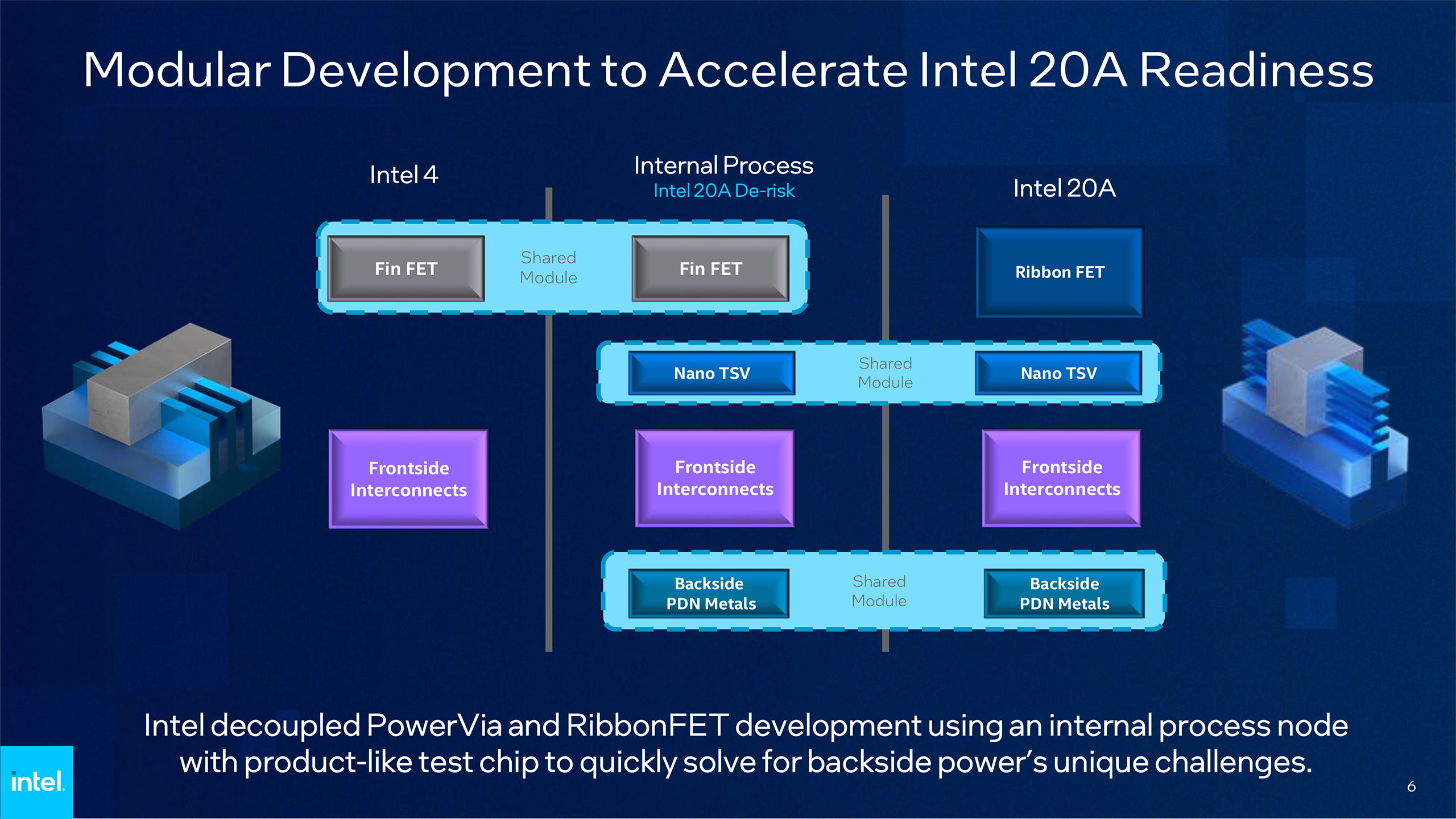

Ahora que Intel ya no es el líder indiscutible del mercado de chips con las mejores tecnologías de proceso, la empresa no podía arriesgarse a un punto potencial de falla en uno de sus nodos de próxima generación. Por lo tanto, desvinculó el desarrollo de los transistores RibbonFET GAA y PowerVia BS PDN para facilitar un poco el proceso de desarrollo al trabajar en RibbonFET con un PDN regular y luego depurar PowerVia con FinFET probados.

Para probar su red de suministro de energía en la parte trasera PowerVia, Intel creó un proceso de fabricación especial basado en su nodo Intel 4 que utiliza transistores FinFET probados, pero viene con un riel de alimentación en la parte trasera en lugar de un riel de alimentación tradicional. Este proceso se llama naturalmente Intel 4 + PowerVia y se utiliza para un chip de prueba cuyo nombre en código es Blue Sky Creek.

El chip de prueba Blue Sky Creek de Intel utiliza dos troqueles, cada uno con cuatro núcleos de bajo consumo basados en la microarquitectura Crestmont. Estos están diseñados para funcionar a 3 GHz a 1,1 voltios. El vehículo de prueba se diseñó solo con dos propósitos: explorar las ventajas de PowerVia BS PDN y eliminar el riesgo de las futuras tecnologías de proceso 20A/18A probando todo lo relacionado con la nueva red de suministro de energía, incluidos los rendimientos, la confiabilidad de PDN y el chip, refrigeración y depuración.

Cuando se trata de rendimientos, Intel dice que la densidad de defectos del chip de prueba implementado en Intel 4 y en Intel 4 + PowerVia es casi la misma. Los objetivos de confiabilidad y características del transistor también cumplieron con las expectativas requeridas para la producción. Además, las térmicas del vehículo de prueba estuvieron en línea con las expectativas. Mientras tanto, Intel admite que la refrigeración será un desafío con la PDN trasera, por lo que ha desarrollado nuevos esquemas de mitigación térmica para enfriar los chips de próxima generación.

«Normalmente, también usa el lado de silicona para disipar el calor», explicó Sell. «Entonces, ahora que ha intercalado sus transistores y la pregunta es: ‘¿Tenemos un problema térmico? ¿Tenemos mucha calefacción local?’ En este punto, probablemente puedas adivinar la respuesta: no».

Podría decirse que la depuración fue una de las partes más complicadas, pero afortunadamente los ingenieros de validación de Intel encontraron una manera de superar las dificultades.

«Hubo muchas preocupaciones y vacilaciones, y eso fue probablemente lo más difícil de resolver: cómo depurar esta nueva entrega de energía trasera», dijo Sell. «Para hacer las cosas aún más desafiantes, el equipo de diseño del chip de prueba agregó intencionalmente algunos errores de ‘huevos de Pascua’ al chip, sin que el equipo de validación lo supiera. ¿La buena noticia? Encontraron los errores. Hemos logrado un gran progreso en los últimos dos años. años desarrollando esas capacidades de depuración y probándolas en Blue Sky Creek».

PowerVia BS PDN de Intel llegará en 2024

Las primeras tecnologías de proceso disponibles públicamente de Intel para usar su red de entrega de energía trasera PowerVia serán sus nodos 20A y 18A que estarán listos para la producción en el segundo semestre de 2023 y el primer semestre de 2024, respectivamente. La primera CPU de cliente de Intel que se fabricará en el proceso de fabricación 20A es Arrow Lake, que se espera que se lance a mediados de 2024 o antes.

Las tecnologías de fabricación 18A y 20A de Intel se desarrollan tanto para los productos de la empresa como para los clientes de Intel Foundry Services, por lo que PowerVia promete ser un beneficio tanto para Intel como para sus clientes de IFS. Si PowerVia BS PDN será o no un beneficio tangible es algo que solo el tiempo dirá, pero cabe señalar que Intel es la primera empresa que está lista para fabricar chips con suministro de energía en la parte trasera, ya que solo se espera que TSMC ofrezca una tecnología similar en finales de 2026 a principios de 2027.