Un entusiasta de la tecnología compartió lo que parece ser una diapositiva interna de TSMC que muestra el progreso del desarrollo del proceso N3E. HS Kuo (se abre en una pestaña nueva) en Twitter. Recientemente, escuchamos de los medios de comunicación de negocios de Taiwán que N3 iba a llegar a la producción en masa en septiembre, pero no hemos tenido mucha información sobre el progreso de N3E desde marzo.

Para recapitular rápidamente, TSMC N3E es una versión ‘Mejorada’ del proceso N3, que inicialmente estaba programado (se abre en una pestaña nueva) (PDF) para producción en masa un año después de N3. Sin embargo, la diapositiva nueva pero sin fecha (por favor agregue una pizca de sal) del Sr. Kuo indica que el desarrollo de N3E está progresando bien e incluso está «por delante de lo planeado».

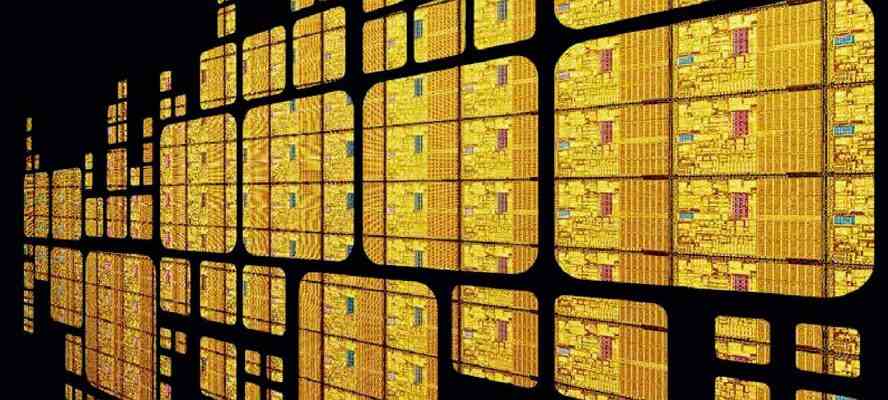

El gráfico sugiere que los rendimientos de N3E SRAM están muy por encima de N3, comenzando unos seis meses antes de la producción de riesgo. Actualmente, se afirma que el rendimiento promedio de SRAM de 256 Mb es de aproximadamente el 80%. También es impresionante que los chips de prueba móviles y HPC rindan alrededor del 80 %. Por último, el rendimiento probado del oscilador en anillo es superior al 92 %.

No nos sorprenden los informes anteriores sobre N3E de que está progresando tan bien. TSMC diseñó N3E con una ventana de proceso mejorada, con una densidad de transistores ligeramente más baja, lo que naturalmente trae el beneficio de mejores rendimientos. Otros beneficios promocionados de N3E son mejores velocidades de reloj y menor consumo de energía.

En otras noticias recientes de 3nm de TSMC, el Commercial Times de Taiwán informa que el fabricante de chips contratado podría haber cambiado de opinión sobre la producción de 3nm en los EE. UU.

Sabemos que TSMC está construyendo una fábrica de 5nm en Arizona, pero anteriormente parecía firme en no querer desarrollar fábricas para sus procesos más avanzados fuera de Taiwán. El rumor es que la aprobación de la Ley de chips de EE. UU. ha inspirado investigaciones e inversiones piloto en una segunda fábrica que generará productos semiconductores de 3 nm. TSMC no ha respondido al informe de Commercial Times.