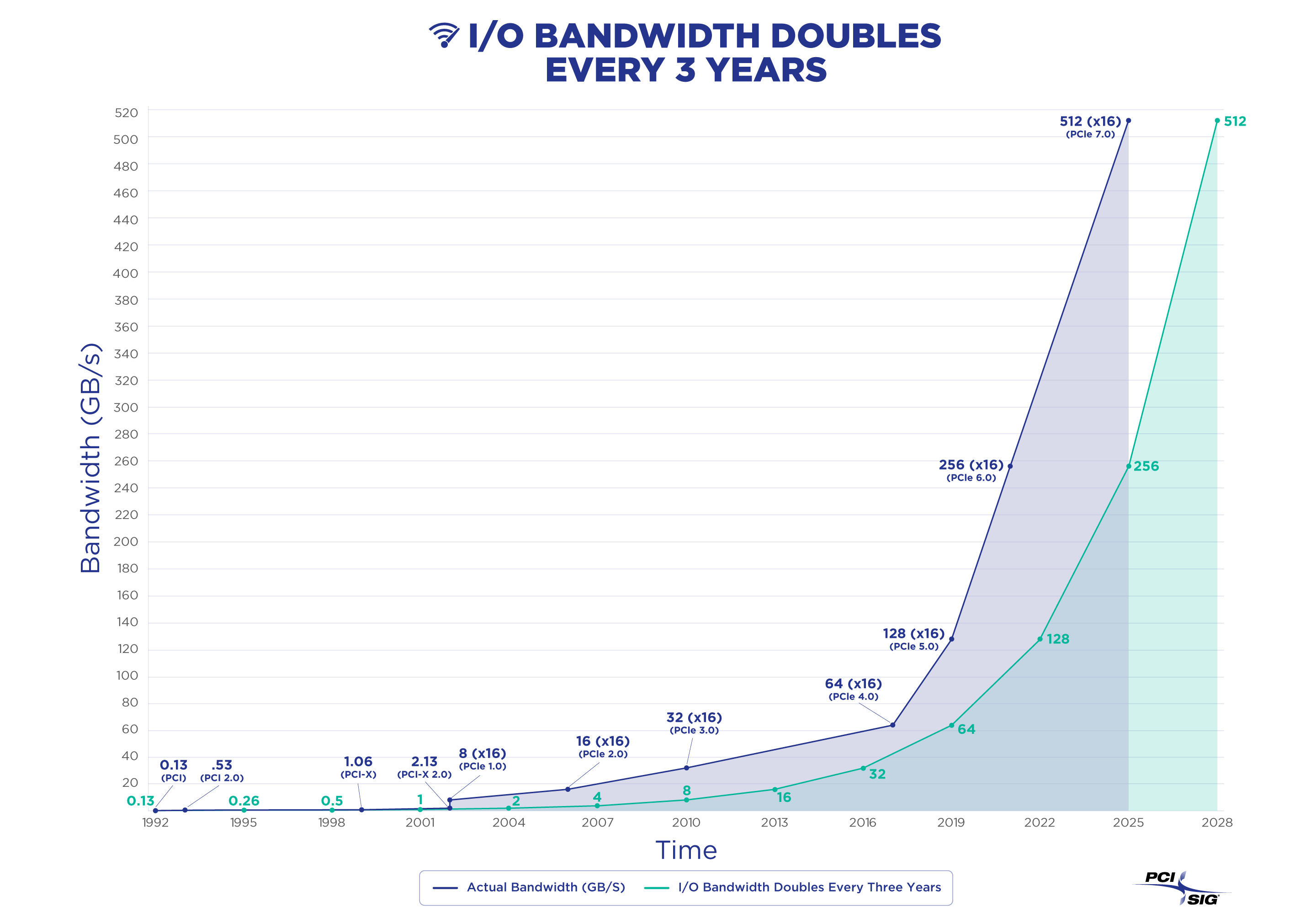

PCI-SIG publicó el martes la versión 0.3 de la especificación PCI Express 7.0, lo que marca un logro significativo para la tecnología que aumentará la tasa de transferencia de datos PCIe a 128 GT/s. Este lanzamiento preliminar indica que los miembros de la organización han acordado las características clave y la arquitectura de la próxima tecnología.

PCIe 7.0 está configurado para mejorar la velocidad de transferencia de datos a 128 GT/s para cada pin, mejorando sustancialmente los 64 GT/s en PCIe 6.0 y los 32 GT/s en PCIe 5.0. Esto implica que una conexión de 16 carriles (x16) puede admitir un ancho de banda bidireccional de 512 GB/s antes de considerar la sobrecarga de codificación. En un intento por aumentar la tasa de transferencia de datos y el ancho de banda, la interfaz PCIe Gen7 está configurada para usar modulación de amplitud de pulso con señalización de cuatro niveles (PAM4), codificación de modo flit 1b/1b y corrección de errores de reenvío (FEC), que son características que el El estándar hereda de PCIe Gen6.

PCI-SIG tiene un proceso de desarrollo de especificaciones muy preciso que consta de varias versiones/puntos de control. La versión 0.3 generalmente carece de detalles, pero proporciona una descripción general de los objetivos previstos y cómo lograrlos. Con respecto a PCIe 7.0, los objetivos principales incluyen una tasa de transferencia de datos de 128 GT/s y soluciones físicas que garanticen una transmisión de datos confiable y eficiente en energía a esta tasa.

Si bien sabemos que la tecnología se basará en PAM4, modo flit y FEC, los detalles sobre la implementación de PCIe Gen7 parecen particularmente interesantes. El cambio a PCIe 7.0, al igual que las transiciones anteriores a PCIe 4.0 y 5.0, requerirá seguimientos de PCIe más cortos debido a las mayores velocidades de señalización. Esto reducirá la distancia permitida entre la raíz y los dispositivos de punto final, como CPU y tarjetas de expansión (tarjetas gráficas, aceleradores, SSD, tarjetas de red) sin componentes como retemporizadores. Por ahora, sabemos que implementar PCIe Gen5 requiere PCB más gruesos y materiales de mayor calidad, lo que significa costos y precios más altos. Sin embargo, no tenemos idea de las consideraciones de costos para PCIe Gen7 a este respecto.

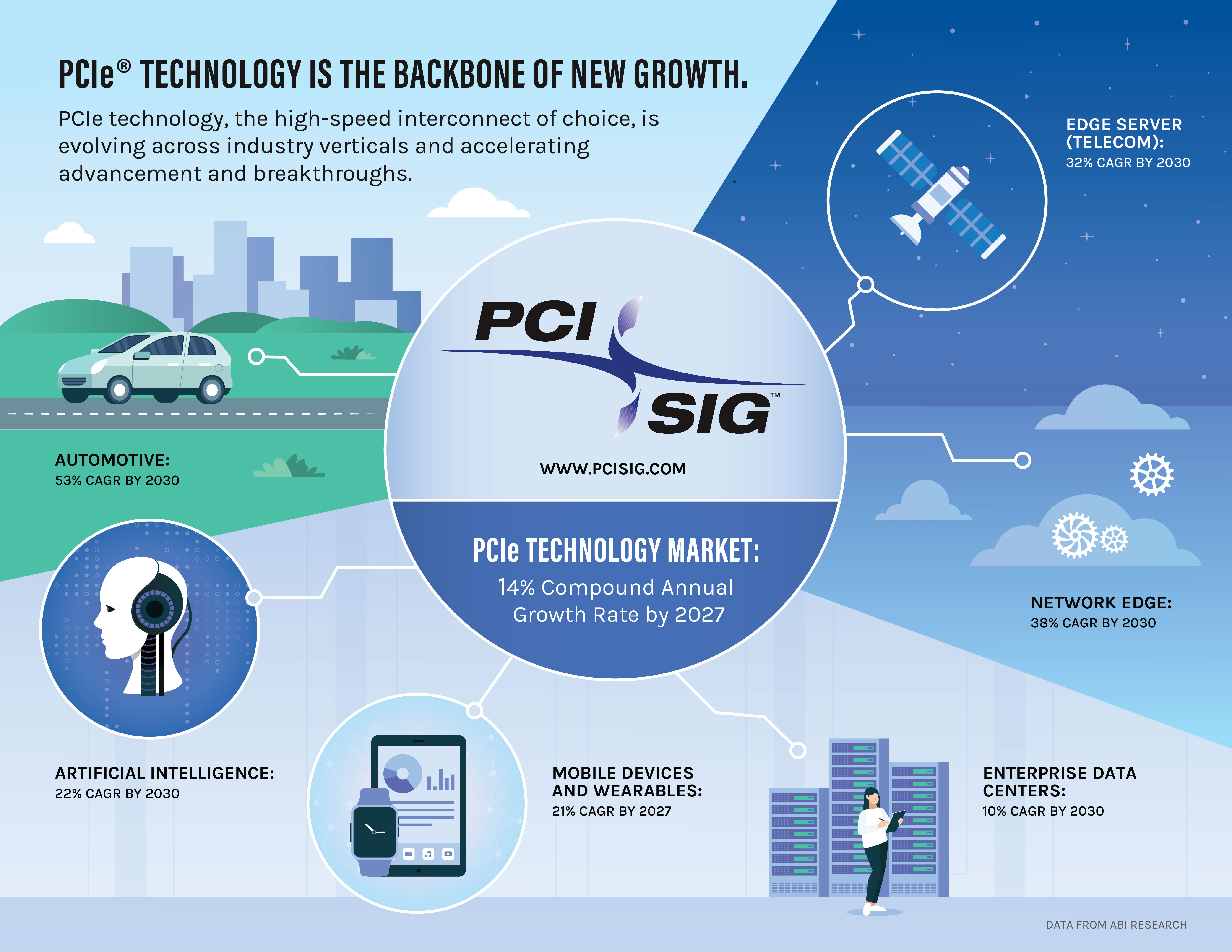

Cabe señalar que PCI-SIG en sí mismo establece claramente que está desarrollando PCIe 7.0 para admitir aplicaciones que consumen mucho ancho de banda como 800G Ethernet, AI/ML, computación en la nube y cuántica, centros de datos de hiperescala, HPC, edge y aeroespacial/militar. Si bien estamos seguros de que PCIe 7.0 eventualmente terminará en las PC de los clientes, PCI-SIG nunca menciona computadoras de escritorio o portátiles.

«La tecnología PCI Express lidera la industria como una interconexión de E/S fundamental y se puede encontrar en todo, desde automóviles hasta servidores de centros de datos», dijo el presidente de PCI-SIG, Al Yanes. «A medida que aumenta la velocidad de la arquitectura PCIe, continuaremos expandiendo nuestras verticales tradicionales mientras nos expandimos a nuevas y emocionantes verticales para satisfacer la demanda de una interconexión de baja latencia y gran ancho de banda».