Si hay un producto tecnológico cuyo escalado no funciona tan bien, es la DRAM. Hay varias razones para esto, la más importante es el diseño real de las celdas DRAM y su relación con la fabricación. Pero según Lam Research, el resultado final de estas dificultades de escalamiento significa que los investigadores en el campo de la DRAM pueden no poder aumentar la densidad de la DRAM dentro de cinco años.

Es en este contexto que Lam Research, una empresa especializada en diseño de circuitos semiconductores, ha publicado una propuesta sobre cómo pueden evolucionar los futuros productos DRAM. Y es muy posible que ese futuro sea el 3D, por lo que parece que los cubos de memoria no están tan lejos del ámbito de las posibilidades. Según la compañía, nos llevará entre cinco y ocho años poder diseñar un dispositivo DRAM 3D fabricable, dejando al mundo con una posible brecha de tres años entre el momento en que finaliza el escalado de DRAM 2D y el momento en que se recupera el escalado de DRAM 3D.

Usando su propiedad SEMulador3D software, Lam Research repitió posibles diseños de DRAM 3D. Su atención se centró en resolver los desafíos de escalado y apilamiento de capas, reducción de capacitores y transistores, conectividad entre celdas y mediante matrices (como TSV de TSMC). [Through Silicon Vias], que ya hemos visto en otros diseños de semiconductores 3D). Finalmente, la empresa estableció los requisitos del proceso que permiten la fabricación del diseño propuesto.

Debido a la forma en que están diseñadas las celdas DRAM, no será posible simplemente colocar componentes DRAM 2D de lado para luego apilarlos uno encima del otro. Esto sucede porque las celdas DRAM tienen una relación de aspecto alta (son más altas que gruesas). Colocarlos de lado requeriría capacidades de grabado (y relleno) laterales que están más allá de nuestra capacidad actual.

Pero cuando comprende la arquitectura en sí, puede cambiarla y adaptarla mientras intenta fluir alrededor de las restricciones de diseño. Sin embargo, es más fácil decirlo que hacerlo, y hay una razón por la que aún no tenemos 3D DRAM.

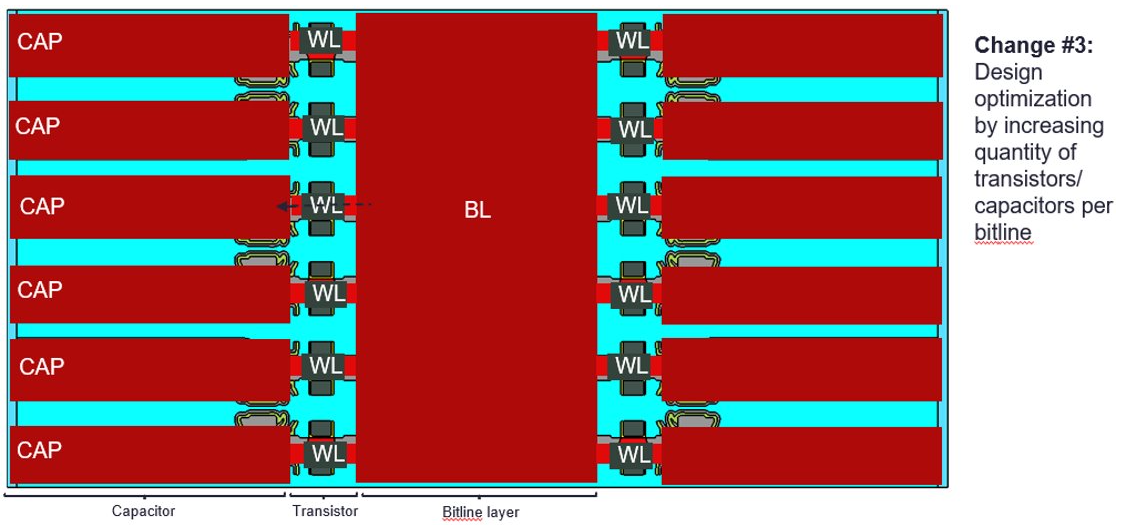

Los diseños actuales de circuitos DRAM necesitan esencialmente tres componentes: una línea de bits (una estructura conductora que inyecta corriente); un transistor que recibe la salida de corriente de la línea de bits y sirve como puerta que controla si la corriente eléctrica puede fluir hacia (y llenar) el circuito; y un condensador, donde la corriente que fluye a través de la línea de bits y el transistor se almacena finalmente en forma de bit (0 o 1).

Lam Research utilizó algunos «trucos» de diseño de chips para llegar a una arquitectura funcional. Por un lado, movieron la línea de bits al lado opuesto del transistor; Debido a que la línea de bits ya no está rodeada por el capacitor, esto significa que se pueden conectar más transistores a la línea de bits, lo que mejora la densidad del chip.

Para maximizar las ganancias en densidad de área, Lam Research también aplicó algunas técnicas de fabricación de transistores de última generación. Estos incluyen diseños de hojas de horquilla Gate-All-Around (GAA), que Intel parece estar explorando para tecnologías de compuerta de próxima generación. La arquitectura DRAM rediseñada propuesta por la investigación de Lam se puede luego apilar, con capas sobre capas del nuevo diseño de celda DRAM una encima de otra en un proceso similar al de NAND.

Pero si bien el escalado de NAND actualmente ronda la marca de 232 capas, Lam Research estima que la primera generación de un diseño de DRAM 3D como el suyo solo aprovecharía hasta 28 capas apiladas. Con las mejoras de la arquitectura y las capas adicionales, Lam Research estima que se puede lograr una mejora de salto de dos nodos en la densidad de DRAM, siendo posibles mejoras adicionales agregando capas adicionales al rascacielos de DRAM. Como hemos visto en otras tecnologías de fabricación, el uso de una matriz vía (la tecnología que sustenta el TSV de TSMC) se utiliza para interconectar capas individuales.

Sin embargo, existe un problema inmediato con el diseño propuesto por Lam Research: actualmente no existen herramientas de fabricación que puedan fabricar de manera confiable las características necesarias. La compañía se apresura a señalar que el diseño de DRAM en sí está a la vanguardia de la actualidad; mejorar y rediseñar herramientas y procesos es un requisito común. Y como dice la compañía, todavía tenemos tiempo antes de llegar al muro de escalamiento de DRAM. Es de esperar que las herramientas y la experiencia necesarias lleguen dentro de ese plazo.