El canal de YouTube Moore’s Law Is Dead filtró dos nuevas diapositivas supuestamente oficiales de AMD que detallan las especificaciones clave y los objetivos de IPC para Zen 5 y Zen 6. Las nuevas diapositivas informan que Zen 5 será una revisión arquitectónica significativa sobre Zen 4, apuntando a mejoras de IPC del 10 al 15%. o más. Según se informa, Zen 5 también incorporará CCX de 16 núcleos por primera vez. Antes de continuar mucho más, tendremos que espolvorear una buena cantidad de sal en este informe.

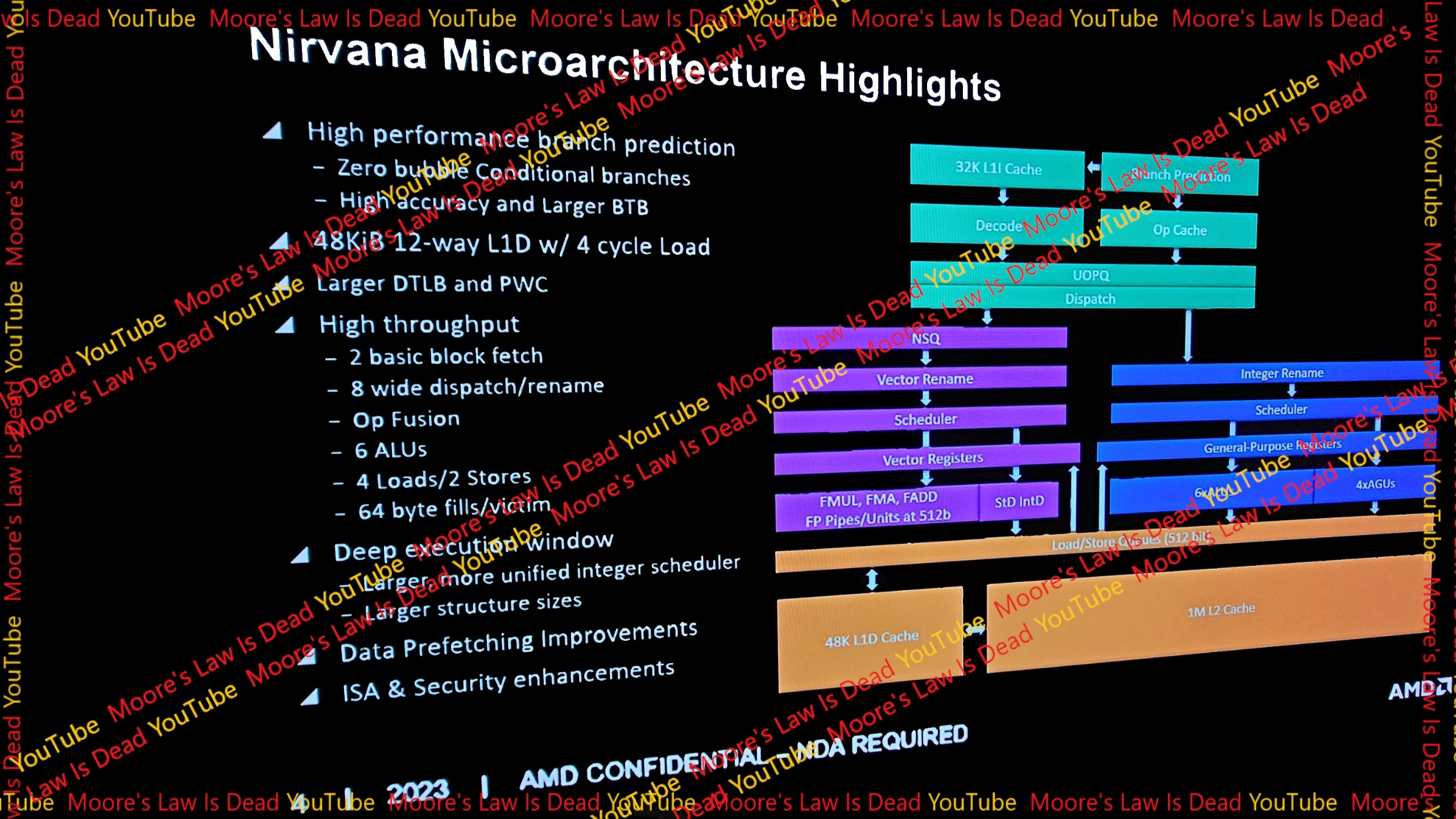

La lista de mejoras del núcleo Zen 5 es bastante extensa. Las mayores ganancias se relacionan con la caché L1, el predictor de bifurcación, la ventana de ejecución y el rendimiento del procesamiento central. El predictor de ramas ha recibido ramas condicionales de burbuja cero, alta precisión y BTB más grande. El tamaño de la caché L1 del Zen 5 ha aumentado de 32 KB en Zen 4 a 48 KB ahora en Zen 5.

Según se informa, el rendimiento del chip se ha mejorado ampliamente, con 2 unidades de recuperación de bloques básicas, 8 unidades de envío/cambio de nombre, 6 ALU, 4 unidades de carga y 2 de almacenamiento, y más. Según se informa, el programador ahora tiene un tamaño de estructura más grande y el programador de números enteros es más grande y más unificado que los diseños anteriores. La diapositiva también enumera mejoras adicionales en la captación previa de datos junto con mejoras de ISA y seguridad, pero no entra en detalles específicos.

Otra mejora considerable revelada en las diapositivas filtradas es la configuración central de los CCX (complejos centrales) del Zen 5, que se han duplicado de 8 a 16. El nuevo cambio marca la primera vez desde Zen 2 que AMD se ha molestado en aumentar el número de núcleos. sus CCX, lo que significa que podríamos ver un «Ryzen 9 8950X» de 32 núcleos en el futuro.

Aún no sabemos qué tipos de núcleos tendrán estos nuevos grupos de núcleos Zen 5. La mitad del número de núcleos de Zen 5 podría dedicarse por completo a los núcleos de eficiencia Zen 5c, o toda la pila podría ser núcleos de rendimiento Vanilla Zen 5. Podría ser una combinación de ambos, ya que las diapositivas de AMD sugieren que habrá diferentes modelos con soporte FP-512 y algunos modelos con núcleos de bajo consumo.

Vale la pena mencionar que estas diapositivas están estrictamente dirigidas a los chips de servidor empresarial (EYPC) de AMD y no se centran en sus CPU de escritorio de consumo convencionales. Así que no espere que todos los detalles lleguen a los chips Ryzen 8000 el próximo año, como la compatibilidad con FP-512. Pero, en general, las especificaciones arquitectónicas subyacentes podrían llegar al Ryzen 8000.

Las diapositivas filtradas también muestran proyecciones adicionales sobre la arquitectura Zen 6 de AMD. La diapositiva muestra que Zen 6 tendrá un objetivo de IPC estimado de al menos el 10% como mínimo, FP16 para IA/aprendizaje automático y un nuevo perfilador de memoria. Finalmente, el último punto menciona que AMD volverá a duplicar el número de núcleos por CCD, pasando de 16 a 32 núcleos. Existe una buena posibilidad de que esta segunda duplicación del recuento de núcleos incluya núcleos de eficiencia Zen 6 más lentos y compactos, pero el hecho de que AMD pueda cuadriplicar el recuento de núcleos en menos de tres generaciones es impresionante de todos modos.

Zen 5 es la arquitectura de CPU de próxima generación de AMD, que se espera que debute en 2024 con los chips móviles y de escritorio de la serie Ryzen 8000 de AMD. Y recuerda, debemos tomar toda esta información con mucha cautela, dado lo lejos que estamos de un lanzamiento oficial.