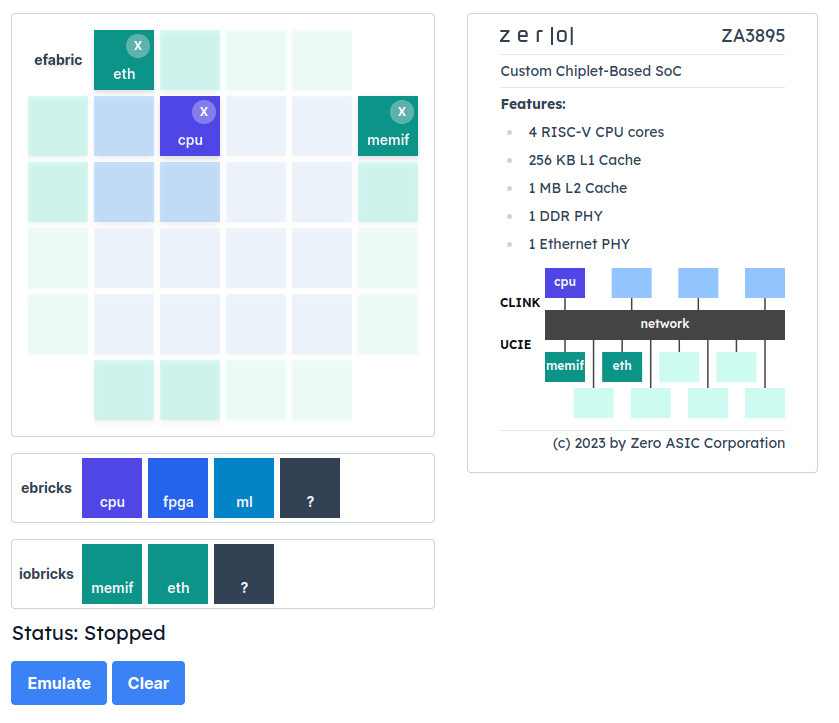

El diseño físico de los procesadores modernos suele tardar años y cuesta decenas o cientos de millones de dólares, dependiendo de la complejidad y la tecnología del proceso. La startup de semiconductores Zero ASIC ha anunciado una plataforma que permite el ensamblaje rápido de un sistema en paquete (SiP) de múltiples chips altamente personalizado a partir de chips en buen estado. La plataforma ChipMaker está destinada a democratizar el desarrollo de silicio personalizado.

Desarrollar un circuito integrado de aplicación específica (ASIC) personalizado desde el concepto hasta la producción es demasiado largo y costoso para muchas empresas emergentes. La plataforma ChipMaker de Zero ASIC simplifica el proceso mediante el uso de diseños basados en chiplets, ocultando las complejidades del diseño de circuitos y permitiendo a los usuarios probar y modificar de forma rápida y precisa sus diseños personalizados antes de ordenar los dispositivos físicos. Todo esto se logra utilizando FPGA (Field Programmable Gate Arrays) en la nube para implementar el código fuente RTL.

La plataforma de Zero ASIC se basa en eFabric, un intercalador 3D que permite la comunicación entre matrices, y eBrick, una colección de chiplets 3D prefabricados con capacidades plug-and-play.

El eFabric actúa como un intercalador 3D dinámico con una estructura similar a una cuadrícula con un ancho de banda de bisección sobre tela de 512 Gb/s/mm. El intercalador 3D facilita la integración de unidades de procesamiento utilizando chiplets eBrick interoperables conectados en 3D con un ancho de banda de chiplet 3D de 128 Gb/s/mm2. También admite la incorporación de funciones IO fuera del paquete a través de chiplets ioBrick basados en UCIe conectados en 2D con un ancho de banda de chiplet 2D de 128 Gb/s/mm.

Por ahora, Zero ASIC tiene un catálogo moderado de chiplets eBrick de 2 mm^2, incluida una CPU de doble núcleo RISC-V de cuatro núcleos compatible con Linux, FPGA integrada 5K LUT, 3 MB de SRAM y 3 TOPS ML (tera-ops por segundo acelerador de aprendizaje automático). Estos chiplets se están utilizando para demostrar las capacidades de la plataforma en la Open Compute Platform Summit/Open Chiplet Economy Center del 17 al 19 de octubre en San José, California.

Zero ASIC espera que el catálogo de chiplets eBrick se expanda significativamente con el tiempo. Esto, a su vez, permitirá que la plataforma ChipMaker sea cada vez más viable, aunque no revela cómo planea lograrlo.

«Los circuitos integrados de aplicaciones específicas (ASIC) personalizados ofrecen una ventaja energética y de costo de 10 a 100 veces mayor que los dispositivos comerciales disponibles en el mercado (COTS), pero el enorme costo de desarrollo hace que los ASIC no sean viables para la mayoría de las aplicaciones», dijo Andreas Olofsson, director ejecutivo y fundador de ASIC cero. «Para construir la próxima ola de dispositivos de silicio que cambiarán el mundo, necesitamos reducir la barrera a los ASIC en órdenes de magnitud. Nuestra misión en Zero ASIC es hacer que pedir un ASIC sea tan fácil como pedir piezas de catálogo a un distribuidor de electrónica».

Ciertamente suena interesante. Queda por ver si realmente funcionará y ganará terreno.