IBM

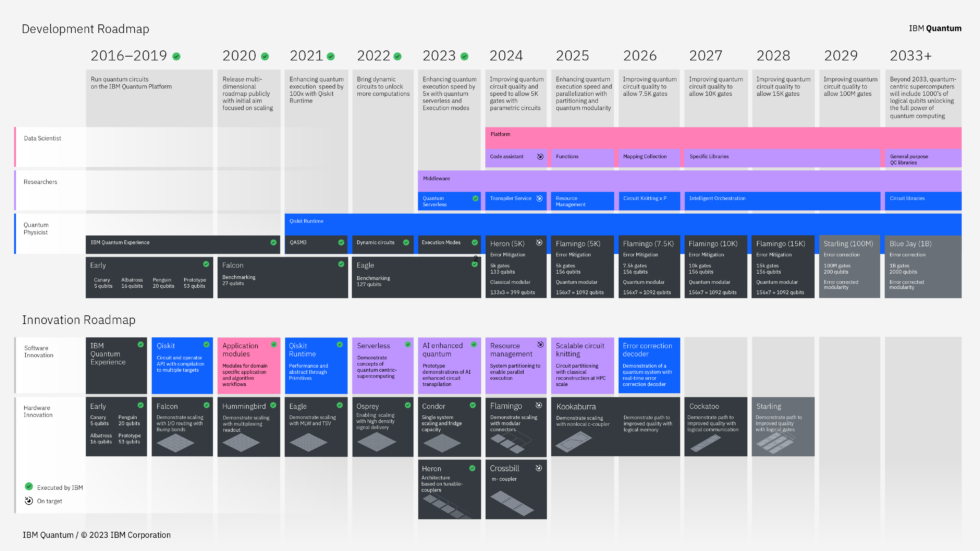

El lunes, IBM anunció que había producido los dos sistemas cuánticos que su hoja de ruta había programado para su lanzamiento en 2023. Uno de ellos se basa en un chip llamado Condor, que es el procesador cuántico basado en transmon más grande lanzado hasta ahora, con 1.121 qubits en funcionamiento. . El segundo se basa en una combinación de tres chips Heron, cada uno de los cuales tiene 133 qubits. Los chips más pequeños como Heron y su sucesor, Flamingo, desempeñarán un papel fundamental en la hoja de ruta cuántica de IBM, que también recibió una importante actualización hoy.

Según la actualización, IBM tendrá qubits con corrección de errores funcionando para finales de la década, gracias a las mejoras en los qubits individuales realizadas a lo largo de varias iteraciones del chip Flamingo. Si bien estos sistemas probablemente no pondrán en riesgo cosas como los esquemas de cifrado existentes, deberían poder ejecutar de manera confiable algoritmos cuánticos que son mucho más complejos que cualquier cosa que podamos hacer hoy.

Hablamos con Jay Gambetta de IBM sobre todo lo que la compañía anuncia hoy, incluidos los procesadores existentes, las hojas de ruta futuras, para qué se podrían usar las máquinas en los próximos años y el software que lo hace todo posible. Pero para entender lo que está haciendo la empresa, tenemos que retroceder un poco y observar hacia dónde se mueve el campo en su conjunto.

Qubits y qubits lógicos

Casi todos los aspectos del trabajo con un qubit son propensos a errores. Establecer su estado inicial, mantener ese estado, realizar operaciones y leer el estado pueden introducir errores que impedirán que los algoritmos cuánticos produzcan resultados útiles. Por lo tanto, uno de los principales objetivos de todas las empresas que producen hardware cuántico ha sido limitar estos errores, y se han logrado grandes avances en ese sentido.

Hay algunos indicios de que esos avances nos han llevado al punto en el que es posible ejecutar algunos algoritmos cuánticos más simples en el hardware existente. Y es probable que este potencial se expanda a otros algoritmos gracias a las mejoras que probablemente podamos esperar en los próximos años.

Sin embargo, a largo plazo, es poco probable que alguna vez consigamos que el hardware qubit llegue al punto en el que la tasa de error sea lo suficientemente baja como para que un procesador pueda completar con éxito un algoritmo complejo que podría requerir miles de millones de operaciones durante horas de cálculo. Para ello, generalmente se reconoce que necesitaremos qubits con corrección de errores. Estos implican difundir la información cuántica contenida en un qubit, denominado «qubit lógico», entre múltiples qubits de hardware. Se utilizan qubits adicionales para monitorear el qubit lógico en busca de errores y permitir su corrección.

Computar utilizando qubits lógicos requiere dos cosas. Una es que las tasas de error de los qubits de hardware individuales deben ser lo suficientemente bajas como para que los errores individuales puedan identificarse y corregirse antes de que se produzcan otros nuevos. (Hay algunos indicios de que el hardware es lo suficientemente bueno para que esto funcione con eficiencia parcial). Lo segundo que necesita son muchos qubits de hardware, ya que cada qubit lógico requiere múltiples qubits de hardware para funcionar. Algunas estimaciones sugieren que necesitaremos un millón de qubits de hardware para crear una máquina capaz de albergar una cantidad útil de qubits lógicos.

IBM ahora dice que espera tener una cantidad útil de qubits lógicos para finales de la década, y Gambetta explicó cómo los anuncios de hoy encajan en esa hoja de ruta.

Qubits y puertas

Gambetta dijo que la compañía ha adoptado un enfoque de dos vías para preparar su hardware. Un aspecto de esto ha sido el desarrollo de la capacidad de fabricar consistentemente grandes cantidades de qubits de alta calidad. Y dijo que el Condor de más de 1.000 qubits es una indicación de que la empresa está en buena forma en ese sentido. «Se trata de qubits aproximadamente un 50 por ciento más pequeños», dijo Gambetta a Ars. «El rendimiento está a la altura: obtuvimos un rendimiento cercano al 100 por ciento».

El segundo aspecto en el que IBM ha estado trabajando es en limitar los errores que ocurren cuando las operaciones se realizan en qubits individuales o en pares. Estas operaciones, denominadas puertas, pueden ser propensas a errores en sí mismas. Y cambiar el estado de un qubit puede producir señales sutiles que pueden transmitirse a los qubits vecinos, un fenómeno llamado diafonía. Heron, el más pequeño de los nuevos procesadores, representa un esfuerzo de cuatro años para mejorar el rendimiento de la puerta. «Es un dispositivo hermoso», dijo Gambetta. «Es cinco veces mejor que los dispositivos anteriores, los errores son mucho menores, [and] La diafonía realmente no se puede medir».

IBM

Muchas de las mejoras se reducen a la introducción de acopladores sintonizables en los qubits, un cambio con respecto al hardware de frecuencia fija que la empresa había utilizado anteriormente. Esto ha acelerado todas las operaciones de las puertas, y algunas han visto un aumento de 10 veces. Cuanto menos tiempo se dedique a hacer algo con un qubit, menos posibilidades habrá de que surjan errores.

Muchas de estas mejoras se probaron en múltiples iteraciones del chip Eagle de la compañía, que se introdujo por primera vez en 2021. La nueva hoja de ruta de la compañía incluirá una iteración mejorada del Heron de 133 qubit lanzada el próximo año que permitirá 5000 operaciones de puerta. A esto le seguirán múltiples iteraciones del procesador Flamingo de 156 qubit del próximo año que llevará las operaciones de puerta a 15.000 para 2028.

Estos chips también se vincularán entre sí en procesadores más grandes como Crossbill y Kookaburra que también aparecen en la hoja de ruta de IBM (por ejemplo, se podrían vincular siete Flamingos para crear un procesador con un número de qubits similar al del Condor actual). La atención se centrará aquí en probar diferentes formas de conectar qubits, tanto dentro como entre chips.