El Centro para el Desarrollo de Computación Avanzada (C-DAC) de la India anunció esta semana[PDF] la primera CPU de computación de alto rendimiento (HPC) de diseño propio del país. Llamado Aum, el primer chip de la India es un diseño de chiplet que puede escalar hasta 96 núcleos y se basa en los diseños V8.4 «Zeus» Neoverse V1 de Arm (los mismos que usa AWS en su Graviton3), y se espera que llegue al mercado como a principios de 2024 en el proceso de 5 nm de TSMC.

Aum se desarrolló como parte de su Misión Nacional de Supercomputación, un programa que tiene como objetivo reducir la exposición de la India a posibles restricciones a la exportación. Con ese fin, el objetivo es implementar una arquitectura de procesador desarrollada a nivel nacional. Sin embargo, tal vez de manera alarmante tanto para Intel como para AMD, el objetivo es que Aum se pueda utilizar tanto en escenarios informáticos de alto rendimiento como en chips informáticos personales. Y donde existe Aum, el mercado es más pequeño.

El razonamiento es simple: si India tiene la capacidad de diseñar chips (ya sea que eso signifique mezclar y combinar piezas de la cartera abierta de Arm o guiar implementaciones específicas para el diseño final fabricable), las posibles restricciones tecnológicas a la exportación podrían ser un poco menores. Al mismo tiempo, la Misión Nacional de Cómputo también tiene como objetivo mejorar la seguridad contra eventuales puertas traseras; un proveedor de diseño neutral como Arm encaja naturalmente en esas preocupaciones. Y si bien controlar el proceso de diseño en sí mismo no lo lleva hasta el final (no cuando los adversarios dispuestos y capaces pueden aplicar puertas traseras en la planta de producción), es un buen comienzo. El uso planificado de software de código abierto para apuntalar un ecosistema de software especializado también pinta un futuro de software más diversificado, por lo que el hardware no es el único segmento que probablemente se fragmente, con el tiempo suficiente.

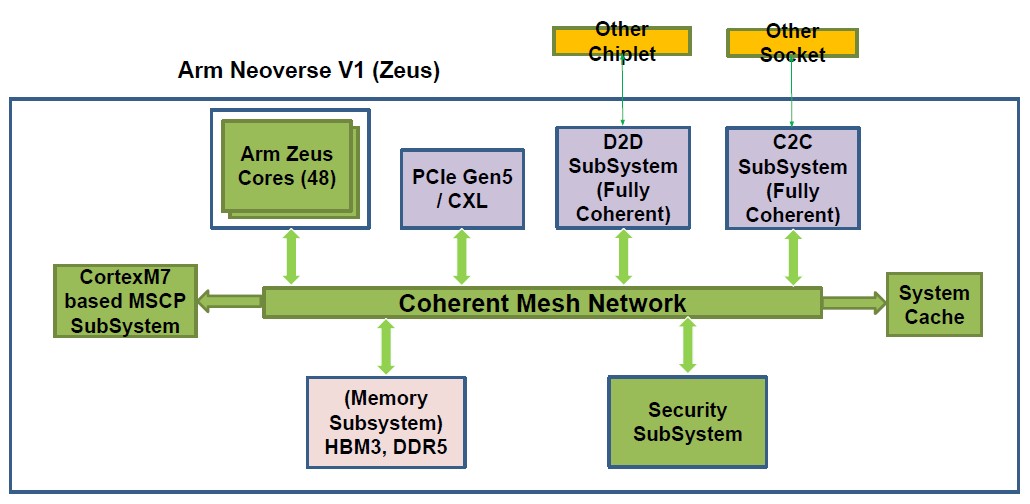

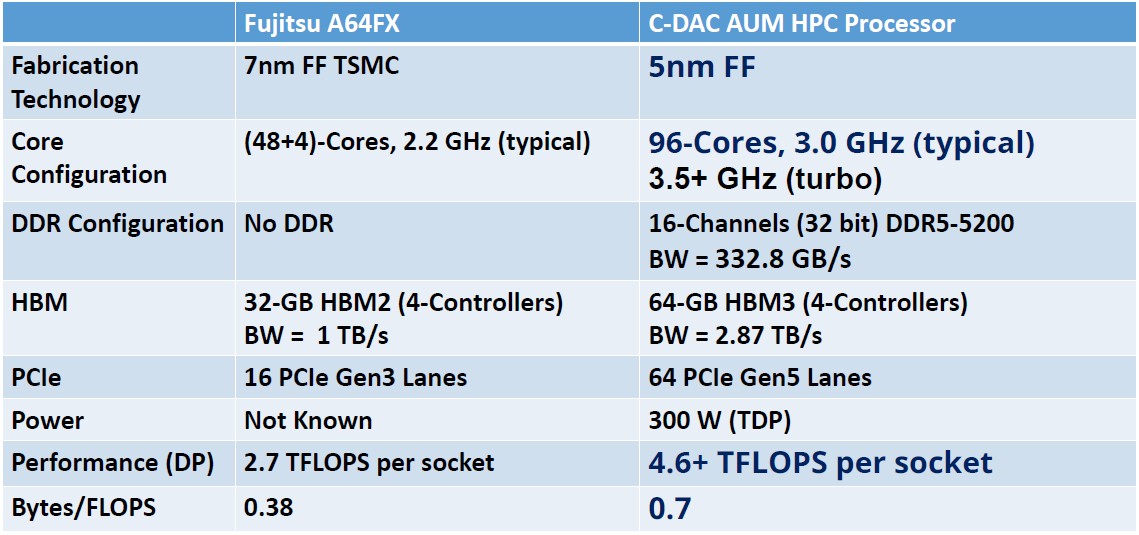

Los chipsets A48Z en el corazón del chip Aum de 96 núcleos cuentan cada uno con 48 núcleos Arm Zeus (3 GHz base, 3,5 GHz Turbo), respaldados por 96 MB de caché L2 de acceso inmediato y otra capa de caché de 96 MB que almacena en búfer los núcleos y el memoria adicional del sistema. En total, cada paquete Aum admite hasta 16 canales de memoria DDR5 (a 5200 MHz, con un ancho de banda de 332,8 GB/s) y 64 GB de memoria HBM3 (6,4 GHz de stock, reducido a 5,6 GHz en el lanzamiento inicial para un asombroso 2,87 TB/s). Los 128 carriles PCIe Gen 5 agregan un rendimiento de bytes adicional, 64 de los cuales habilitan aceleradores adicionales (como aceleradores GPU o FPGA).

Es probable que los 64 restantes estén enrutados para la estructura de comunicaciones interna del chip, una red de malla coherente de estilo NUMA, enlaces totalmente coherentes con la memoria basados en el protocolo CCIX. Este enlace es utilizado por dos sockets Aum para comunicarse, y requiere una o dos páginas de diseño de Infinity Fabric de AMD.

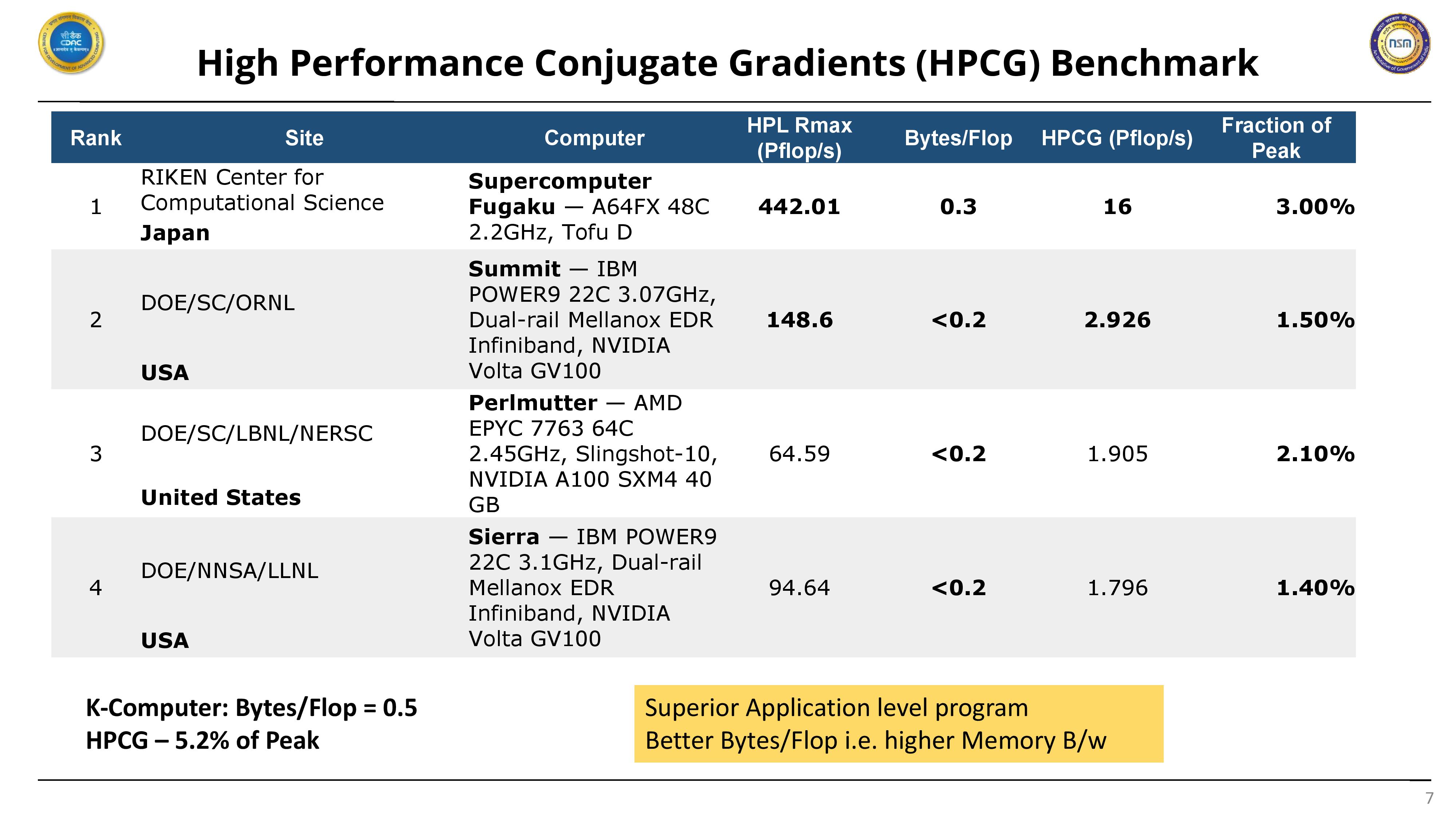

Según la documentación, el diseño de Aum tiene como objetivo principal aumentar la cantidad de ancho de banda de memoria disponible por flop de potencia informática (la relación byte/flop), que se ha encontrado que es un factor altamente limitante en la escala de rendimiento para el cálculo de HPC. Demasiados automóviles (operaciones flotantes por segundo) en muy pocos carriles (rendimiento de memoria) solo pueden terminar de una manera. El resultado es que Aum y su arquitectura Arm tienen como objetivo un rendimiento de 4,6 teraflops por socket y 3 TB/seg de ancho de banda de memoria agregado. Eso le dará una relación byte/flop de 0,7, mucho más alta que la de 0,38 alcanzada por la supercomputadora Arm más rápida del mundo, la japonesa Fugaku, y superando decisivamente a la estadounidense IBM y Summit basada en Nvidia (<0,2 bytes/flop). Sin embargo, con un TDP esperado de 300 W, parece que la eficiencia energética en realidad disminuyó en comparación con los núcleos A64FX Arm de Fugaku.

Si todo va según lo planeado, la CPU Aum Arm de India será una entrada sólida en el campo de la supercomputación. Crucialmente, será uno de cosecha propia, aunque no de manera dramática, al menos en sus primeras iteraciones. Claramente, se puso mucho trabajo en el avance del subsistema de memoria en su conjunto y, en general, la memoria es más fácil y está más disponible para la fuente que los chips Aum de 5 nm de TSMC. Personalizar el núcleo de la CPU en sí mismo podría ser el próximo paso de C-DAC, preparando el camino para India y agregando impulso al proceso de «nacionalización de chips» en otros países. China también ha tenido interés en Arm, por cierto; pero esa es una historia completamente diferente.

Este impulso más amplio para un ecosistema de chips más variado es parte de la razón por la cual Intel decidió reinvertir en su negocio de chips cliente Foundry, un movimiento que su rival AMD hizo hace años (mientras se encontraba en medio de una de sus reestructuraciones corporativas más difíciles) . Y es otra victoria más para el ecosistema Arm en comparación con su alternativa x86, a veces problemática, que en sí misma también castiga a algunos más que a otros.

También es, quizás, una señal de lo que vendrá en lo que respecta a los volúmenes de envío para los fabricantes de semiconductores: cada vez más entidades están lanzando y recibiendo sus diseños de las aguas de TSMC, pero solo hay obleas para todos los interesados, y migajas. Las peleas de volumen ya están tirando basura por el suelo.

A continuación se muestra la plataforma de diapositivas completa.