Intel

Los procesadores Intel para portátiles Meteor Lake de próxima generación están a punto de lanzarse: la compañía anunció esta semana que los primeros procesadores se lanzarán el 14 de diciembre. No está claro si los sistemas Core y Core Ultra reales estarán disponibles para comprar en esa fecha, pero como mínimo. , el anuncio oficial allanará el camino para muchos anuncios de portátiles en el CES en enero.

Ya conocemos muchos datos básicos sobre Meteor Lake; Utiliza una combinación de chiplets fabricados por Intel y TSMC en lugar de una única matriz monolítica, y marcará el retiro de la “enésima generación” de Intel y de las marcas i3/i5/i7/i9. También sabemos que no estará listo para computadoras de escritorio y que la próxima ronda de CPU de escritorio Core será muy similar a los chips de 12.ª y 13.ª generación.

Pero en el evento de Innovación de Intel de esta semana, la compañía profundizó un poco más en algunos de los avances de Meteor Lake, describiendo más sobre cómo los chips equilibrarían los núcleos E y P y anunciando su actualización de GPU integrada más sustancial en años. A continuación veremos algunos aspectos destacados, aunque vale la pena verlos o leer la presentación completa para obtener más información.

Azulejos por millas

Intel

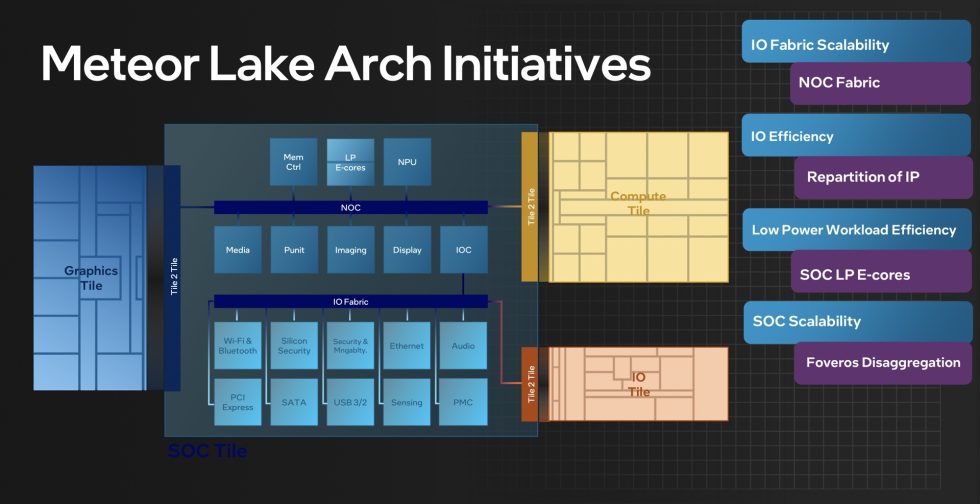

Meteor Lake será el primer procesador de consumo de Intel en pasar a un diseño basado en chiplets; en lugar de ser un troquel monolítico que contiene la CPU, la GPU y todos los demás bits y piezas necesarios para una CPU de computadora portátil moderna, Meteor Lake se divide en cuatro. «baldosas» que se unen entre sí mediante una quinta loseta base que les permite comunicarse entre sí. El proceso de apilar los chiplets encima del mosaico base es una tecnología de empaquetado que Intel llama Foveros.

Aquí hay un desglose básico de lo que hay en cada uno de esos cuatro mosaicos:

-

- El mosaico de cálculo es donde está la mayor parte de la CPU real. Las representaciones actuales de Intel muestran un chip con seis núcleos P de alto rendimiento basados en la arquitectura Redwood Cove y ocho núcleos E de alta eficiencia basados en la arquitectura Crestmont.

- El mosaico de gráficos Es donde ocurre la mayor parte del procesamiento de gráficos, aunque algunas funciones específicas que normalmente encontrarías en una GPU se han movido a otros mosaicos. La GPU integrada de Meteor Lake es principalmente una versión integrada de una GPU dedicada Intel Arc, completa con aceleración de trazado de rayos por hardware.

- El mosaico IO maneja la mayoría de la conectividad externa, incluidas las líneas PCI Express 5.0 y la compatibilidad con Thunderbolt 4 (Thunderbolt 5 deberá esperar).

- El mosaico de SoC Es probablemente el más interesante de los cuatro. Incluye dos Crestmont E-cores adicionales, el motor de codificación y decodificación de medios que normalmente estaría ubicado en la GPU y la unidad de procesamiento neuronal (NPU) utilizada para acelerar las cargas de trabajo de IA y aprendizaje automático. También maneja la conectividad Wi-Fi y Bluetooth y la conexión a pantallas externas a través de HDMI 2.1 y DisplayPort 2.1.

Una de las cosas notables de Meteor Lake es que no todos los mosaicos son fabricados por Intel. El mosaico de cómputo, que alberga los núcleos P reales y la mayoría de los núcleos E, utiliza el nuevo proceso Intel 4, una actualización del proceso Intel 7 utilizado para la mayoría de los chips Core actuales. Pero el mosaico de gráficos se fabrica en un proceso TSMC de 5 nm, mientras que el mosaico IO y el mosaico SoC se fabrican en un proceso TSMC de 6 nm.

Intel también ha utilizado la fabricación de TSMC para fabricar sus GPU Arc, por lo que no es la primera vez que vemos a estos dos enemigos de la fabricación de chips trabajar juntos. Pero Intel está tratando de ponerse al día con la fabricación de TSMC e Intel considera que sus operaciones de fundición son clave para su crecimiento futuro. No me sorprendería que el objetivo final sea volver a los mosaicos totalmente fabricados por Intel.

Incluso más núcleos electrónicos

Intel

Intel ha dicho que los núcleos P de Meteor Lake no cambian mucho en comparación con los utilizados en las CPU Alder Lake y Raptor Lake de 12.a y 13.a generación; es posible que veamos velocidades de reloj más altas, pero no ha cambiado mucho en términos de instrucciones. por reloj o conjunto de instrucciones. Sin embargo, los E-cores obtienen algunas mejoras.

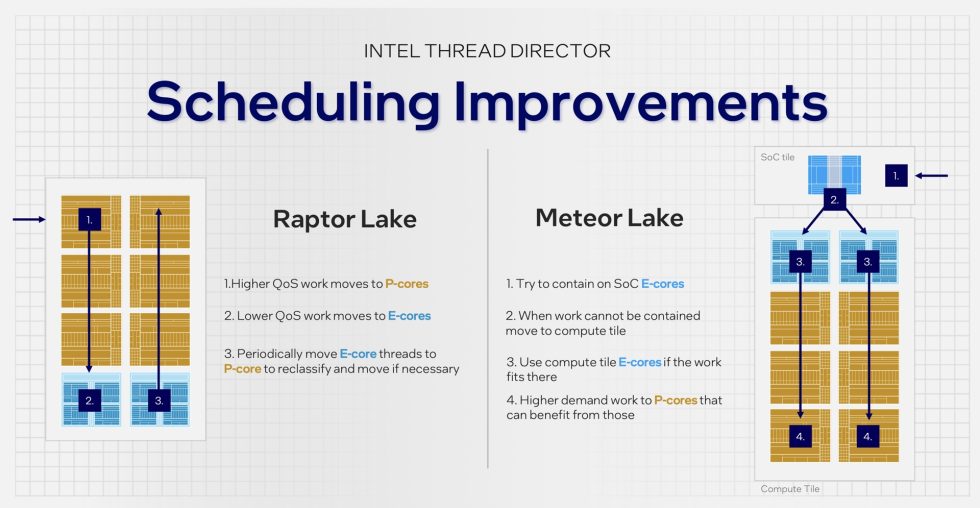

Meteor Lake en realidad incluye dos tipos diferentes de E-cores. Hay dos núcleos E de bajo consumo (LP) en el mosaico de SoC, y la versión actualizada de Thread Director de Intel intentará utilizar esos núcleos E para tantas tareas como sea posible. Intel llama a esta parte del mosaico de SoC la «isla de bajo consumo» porque la idea es permitir que el mosaico de cómputo y el mosaico de gráficos se apaguen por completo tanto como sea posible para ahorrar energía.

Cuando las tareas requieren más rendimiento del que los núcleos E de LP pueden proporcionar, Thread Director las enviará al mosaico de cómputo, ya sea a los clústeres principales de núcleos E, que están ajustados para manejar cargas de trabajo multiproceso de bajo impacto, o a los núcleos P. , que se utilizan para tareas de un solo subproceso y cualquier trabajo de subprocesos múltiples que los E-cores no puedan manejar. Este es un cambio con respecto a la forma en que funciona Thread Director en los procesadores de 12.ª y 13.ª generación, donde las tareas de alta prioridad se dirigirían directamente a los núcleos P sin probar primero los núcleos E. (Aunque queda por ver si los cambios en Thread Director resultarán en algún tipo de retrasos perceptibles por el usuario para tareas de alto rendimiento).

Intel

También vale la pena señalar: los Crestmont E-cores se pueden agregar a los procesadores en grupos de dos, mientras que los Gracement E-cores de la generación anterior solo se podían agregar en grupos de cuatro. Esto podría hacer que a Intel le resulte más fácil justificar la incorporación de pequeños grupos de E-cores a procesadores de gama baja que no los tenían antes. Todos los núcleos E siguen siendo de un solo subproceso, mientras que los núcleos P aún admiten dos subprocesos por núcleo.

Los nuevos E-cores también incluyen algunas otras sutilezas: instrucciones VNNI para acelerar cargas de trabajo de IA e incluso AVX10, que brinda muchos de los beneficios de las instrucciones AVX-512 de Intel sin requerir registros de 512 bits. Los procesadores Core de 12.ª y 13.ª generación desactivaron totalmente la compatibilidad con AVX-512 porque los E-cores no lo admitían, a pesar de que la compatibilidad era presente en los núcleos P. Esto ha creado una situación incómoda en la que los últimos chips Zen 4 de AMD admiten las instrucciones AVX-512 que Intel inventó y promovió, mientras que los últimos chips de consumo de Intel no lo hacen.