Es posible que Samsung no tenga mucho éxito con su proceso GAA de 3 nm, pero tiene la intención de hacer las paces con su tecnología de 2 nm de próxima generación, que se dice que entrará en producción en masa el próximo año. Para obtener una ventaja frente a su rival de fundición TSMC, un nuevo informe afirma que el gigante coreano está introduciendo la tecnología Backside Power Supply (BSPDN), que tiene como objetivo ofrecer varios beneficios, que discutiremos aquí.

La tecnología BSPDN supuestamente se probó con dos núcleos ARM, y Samsung logró reducir el área del chip de ambos en diversos grados.

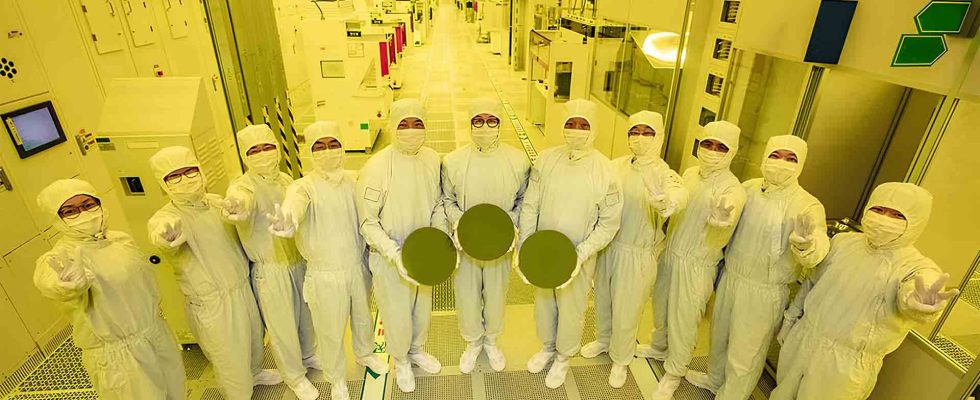

Será un enfrentamiento competitivo entre Samsung y TSMC, ya que ambos pretenden presentar la mejor versión de sus nodos de 2 nm. Para Samsung, un informe de Chosun afirma que se espera que la tecnología Backside Power Supply cambie las reglas del juego y que los resultados de las pruebas iniciales han superado el objetivo de la empresa. En cuanto a las pruebas específicas, se dijo que Samsung aplicó esta tecnología a dos núcleos ARM sin nombre, con el área del chip reducida en un 10 por ciento y un 19 por ciento.

Con el área del chip reducida, Samsung puede comenzar efectivamente a producir en masa diseños de SoC que promocionan un área de superficie más pequeña, y no solo eso, las pruebas anteriores realizadas ayudaron a mejorar considerablemente el rendimiento y los niveles de eficiencia energética. Como indica el informe, BSPDN es un proceso nuevo que aún no se ha comercializado, aunque no se menciona si esto se debió a limitaciones de costos o si no se pensó mucho en explorar esta tecnología.

En cualquier caso, como su nombre indica, Backside Power Supply son líneas de alimentación colocadas en la parte posterior de la oblea, que separa el circuito y el espacio de la fuente de alimentación. Esto ayuda a maximizar la eficiencia y también existe la oportunidad de mejorar el rendimiento de los semiconductores. Actualmente, las líneas eléctricas se colocan en la parte superior de las obleas, ya que es allí donde se dibuja el circuito y crea una gran comodidad para el fabricante. Sin embargo, a medida que los circuitos se vuelven más refinados y Samsung y TSMC comienzan a explorar nodos avanzados como los de 2 nm, cada vez es más difícil grabar circuitos y líneas eléctricas en un lado.

Con el tiempo, lo que sucederá es que a medida que la brecha del circuito se reduzca, se producirán interferencias, lo que generará más dificultades tanto en el diseño como en la producción en masa. Ya se dice que Samsung obtuvo el primer pedido de chips de 2 nm de una startup japonesa, pero no está claro si la tecnología BSPDN se aplicó a este lote. No hay noticias de que TSMC esté experimentando con la fuente de alimentación trasera, por lo que, en el papel, Samsung tiene una ventaja aquí, aunque el tiempo dirá qué tan exitoso es este enfoque.

Fuente de noticias: Chosun