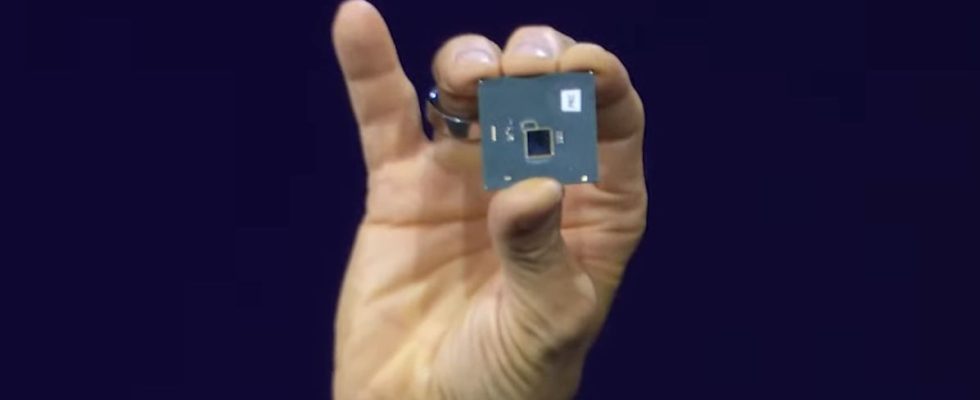

El director ejecutivo de Intel, Pat Gelsinger, mostró el primer procesador basado en chiplets conectado a UCIe del mundo aquí en Innovation 2023, lo que marca la primera exhibición pública de silicio habilitado para UCIe en funcionamiento. El chip cuenta con un chiplet Intel UCIe IP fabricado en su propio nodo de proceso Intel 3 emparejado con un chip Synopsys UCIe IP fabricado en el nodo TSMC N3E de vanguardia. Los dos chiplets se comunican a través de la interfaz EMIB de Intel.

La interfaz Universal Chiplet Interconnect Express (UCIe) es compatible con una amplia gama de incondicionales de la industria, como Intel, AMD, Arm, Nvidia, TSMC y Samsung, entre otros 120. Esta interconexión está diseñada para estandarizar las interconexiones entre chiplets con un diseño de código abierto, reduciendo así costos y fomentando un ecosistema más amplio de chiplets validados.

Los paquetes multichiplet actuales utilizan interfaces y protocolos propietarios para comunicarse entre sí, lo que hace que la adopción generalizada de chiplets de terceros sea una tarea desalentadora. El objetivo de UCIe es crear un ecosistema con una interfaz estandarizada para que algún día los fabricantes de chips puedan simplemente seleccionar chipsets de otros diseñadores e incorporarlos a sus nuevos diseños con un mínimo de trabajo de diseño y validación.

El consorcio UCIe se creó el año pasado (más detalles aquí) y ya ha disfrutado de un amplio apoyo para la industria de fabricación de chips. La especificación debutó en la versión 1.0, pero ahora pasó a la especificación 1.1 descrita en el álbum anterior. El consorcio ha delineado objetivos de rendimiento y área muy agresivos, dividiendo los mercados objetivo en dos amplias gamas, con técnicas de empaquetado 2D estándar y técnicas 2,5D más avanzadas (EMIB, CoWoS, etc.). Naturalmente, las opciones de empaquetado avanzadas proporcionan mayor ancho de banda y densidad.

Los procesadores basados en chiplets de Intel, como Sapphire Rapids y el recientemente anunciado Meteor Lake, utilizan actualmente una interfaz y un protocolo patentados para la comunicación entre los chiplets, pero Intel ha anunciado que utilizará la interfaz UCIe después de sus procesadores de consumo Arrow Lake de próxima generación. AMD y Nvidia también están trabajando en sus propias iniciativas y puede leer sobre esos esfuerzos en esos enlaces. Ninguno de los dos ha demostrado que el silicio funcione.

Estamos aquí en la feria y actualizaremos con detalles adicionales sobre el chip de prueba a medida que surjan.