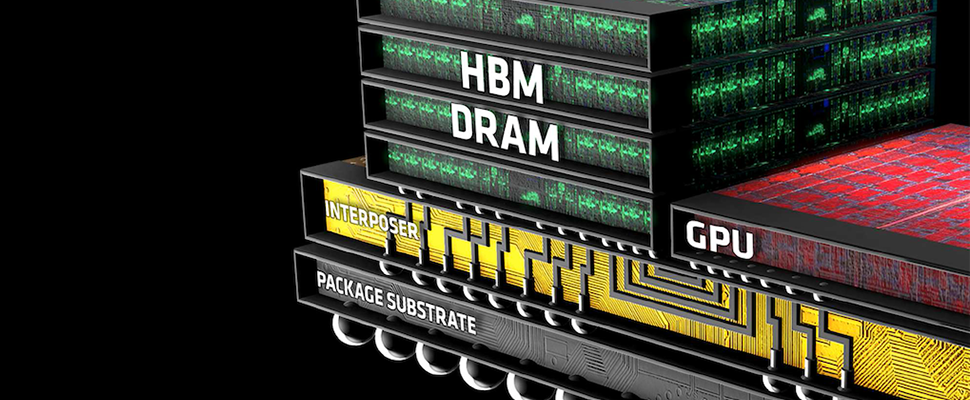

Hemos oído hablar de la memoria HBM4 varias veces en los últimos meses, y esta semana Samsung reveló que espera que HBM4 se introduzca en 2025. La nueva memoria contará con una interfaz de 2048 bits por pila, el doble de ancha que la de 1024 bits de la HBM3. poco.

«De cara al futuro, se espera que HBM4 se introduzca en 2025 con tecnologías optimizadas para altas propiedades térmicas en desarrollo, como el ensamblaje de película no conductora (NCF) y la unión híbrida de cobre (HCB)», SangJoon Hwang, vicepresidente ejecutivo y director de productos DRAM. y equipo de tecnología de Samsung Electronics, escribió en una publicación del blog de la empresa.

Aunque Samsung espera que HBM4 se introduzca en 2025, su producción probablemente comenzará en 2025-2026, ya que la industria deberá prepararse bastante para esta tecnología. Mientras tanto, Samsung ofrecerá a sus clientes sus pilas de memoria HBM3E con una velocidad de transferencia de datos de 9,8 GT/s que ofrecerá un ancho de banda de 1,25 TB/s por pila.

A principios de este año, Micron reveló que la memoria ‘HBMNext’ surgiría alrededor de 2026, proporcionando capacidades por pila de entre 32 GB y 64 GB y un ancho de banda máximo de 2 TB/s por pila o más, un marcado aumento con respecto a los 1,2 TB/s por pila de HBM3E. . Para construir una pila de 64 GB, se necesitará una pila de 16 Hola con dispositivos de memoria de 32 GB. Aunque los stacks 16-Hi son compatibles incluso con la especificación HBM3, nadie ha anunciado este tipo de productos hasta ahora y parece que estos stacks tan densos sólo llegarán al mercado con HBM4.

Para producir pilas de memoria HBM4, incluidas pilas de 16 Hi, Samsung necesitará pulir un par de nuevas tecnologías mencionadas por SangJoon Hwang. Una de estas tecnologías se llama NCF (película no conductora) y es una capa de polímero que protege los TSV en sus puntos de soldadura del aislamiento y los golpes mecánicos. Otra es HCB (unión de cobre híbrida), que es una tecnología de unión que utiliza un conductor de cobre y una película aislante de óxido en lugar de soldadura convencional para minimizar la distancia entre dispositivos DRAM y permitir los golpes más pequeños necesarios para una interfaz de 2048 bits.