En el Simposio de Tecnología de América del Norte de 2023, TSMC reveló más información sobre sus próximas tecnologías de proceso de clase de 2 nm que estarán listas para la producción en 2025-2026. La fundición más grande del mundo planea expandir su familia N2 con N2P que obtendrá un riel de alimentación en la parte trasera y promete para aumentar el rendimiento, reducir el consumo de energía y aumentar la densidad del transistor. Además, TSMC planea N2X, un nodo diseñado para brindar el máximo rendimiento y soporte para voltajes más altos.

N2 proporciona ventajas de nodo completo

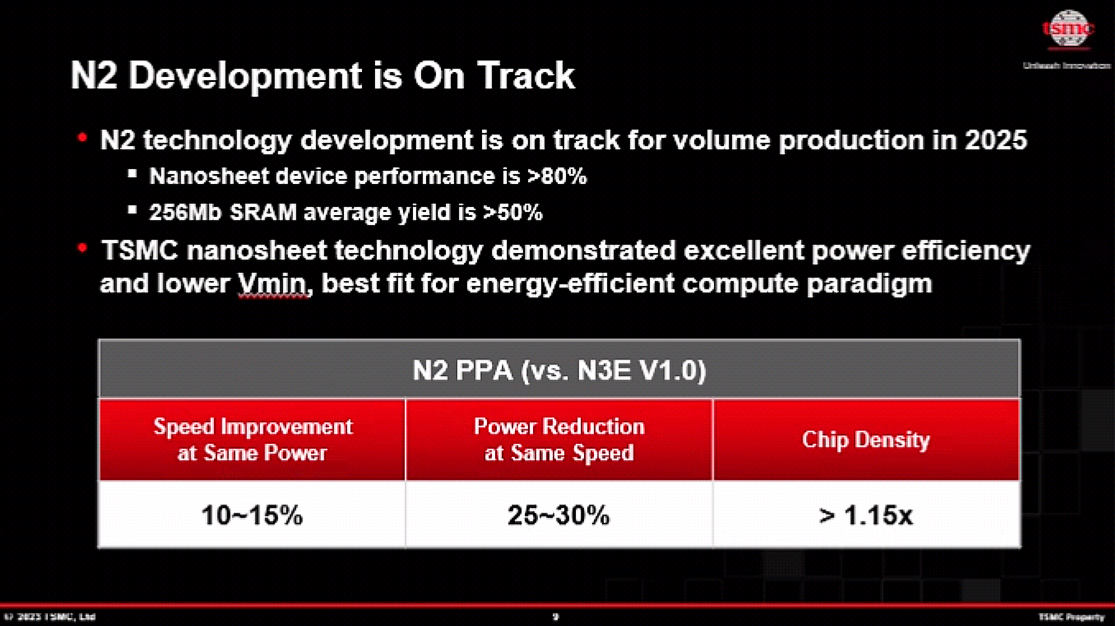

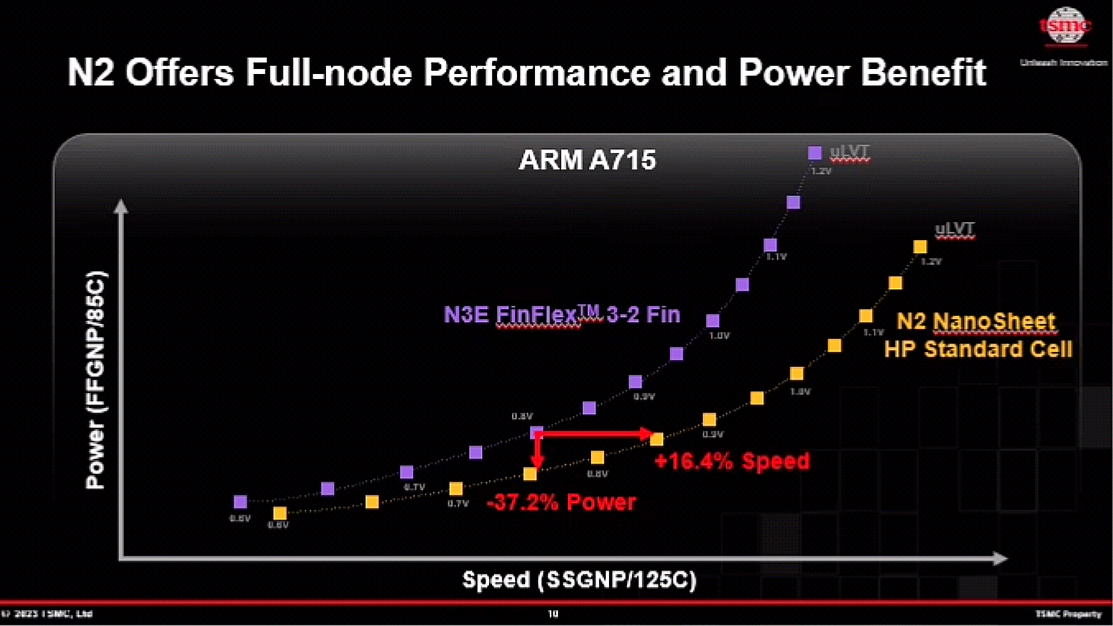

La tecnología de proceso N2 original de TSMC, que entrará en producción de gran volumen en algún momento de 2025, presenta transistores de nanoláminas gate-all-around (GAA). En comparación con N3E, el nuevo nodo promete aumentar el rendimiento entre un 10 % y un 15 % con una potencia y un número de transistores idénticos, o reducir el consumo de energía entre un 25 % y un 30 % manteniendo la misma frecuencia y complejidad. Cuando se trata de escalar, TSMC se abstiene de proporcionar números detallados, pero dice que la nueva tecnología de fabricación permitirá un aumento de la densidad del chip en un 15 %, que es un término ambiguo, ya que refleja un circuito integrado hipotético que contiene un 50 % de lógica y un 30 % de SRAM. , y 20% circuitos analógicos.

El progreso de N2 de TSMC parece estar según lo planeado. En su simposio, TSMC anunció que el rendimiento de su transistor Nanosheet GAA había alcanzado más del 80 % de sus especificaciones objetivo y que el rendimiento promedio de un IC de prueba SRAM de 256 Mb supera el 50 %.

N2P: Power Rail trasero para una mayor eficiencia de rendimiento

Si bien N2 ofrece ventajas tangibles sobre N3E, su sucesor, N2P, promete ser aún más impresionante. El proceso de clase de 2nm de segunda generación de TSMC está configurado para incorporar una red de suministro de energía (PDN) trasera que está diseñada para aumentar el rendimiento del transistor, reducir el consumo de energía, aumentar la densidad del transistor y eliminar los riesgos de interferencia entre los cables de datos y de alimentación en el chip.

La entrega de energía trasera es una de las innovaciones más importantes de los últimos años, ya que las resistencias de contacto y de final de línea (BEOL) han sido los principales desafíos de los fabricantes de chips durante un tiempo. Al reubicar los rieles de alimentación en la parte posterior de la oblea, la entrega de energía en la parte posterior separa las E/S y el cableado de alimentación y mitiga los problemas de resistencia elevados en el BEOL.

Aunque TSMC no ha proporcionado cifras específicas con respecto a los beneficios de rendimiento, potencia y área (PPA) de N2P sobre N2, algunos analistas dicen que la PDN trasera podría conducir a una disminución del consumo de energía de un solo dígito y un aumento de la densidad del transistor de dos dígitos. Teniendo en cuenta que es probable que TSMC realice más optimizaciones en N2P, espere que esta tecnología sea significativamente más avanzada que N2 y N3, tanto en términos de eficiencia de rendimiento como en densidad de transistores.

TSMC espera que N2P esté listo para la fabricación de alto volumen (HVM) en 2026, así que espere que los chips reales fabricados en este nodo se envíen en 2027. Suponiendo que Intel cumpla su promesa y envíe los primeros chips fabricados en sus tecnologías de producción 20A (que emplea tanto Transistores RibbonFET GAA y PDN trasero PowerVia) en 2024, estará dos o tres años por delante de TSMC con riel de alimentación trasero.

N2X: altos voltajes para un rendimiento extremo

TSMC está desarrollando N2X, un proceso de fabricación diseñado para aplicaciones informáticas de alto rendimiento (HPC), como CPU de centro de datos de gama alta. En general, estos chips consumen mucha energía y necesitan la capacidad de aumentar sus relojes en los picos de demanda. Esto significa que tienen que soportar altas tensiones y corrientes. Dado que el nodo está configurado para estar disponible en 2026 como muy pronto, TSMC no describe sus mejoras de rendimiento sobre N2, N2P y N3X en este momento. Mientras tanto, al igual que con todas las tecnologías de producción recientes, el máximo rendimiento y eficiencia solo se puede lograr a través de una extensa optimización conjunta de tecnología de diseño (DTCO) entre la fundición y los desarrolladores de IP.